WAIKATO Research Commons

### http://researchcommons.waikato.ac.nz/

### Research Commons at the University of Waikato

### **Copyright Statement:**

Te Whare Wānanga o Waikato

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

The thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of the thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from the thesis.

## Development of a Power Factor Corrected High Current Supercapacitor Charger for a Surge Resistant UPS

A thesis submitted in partial fulfillment of the requirement for the degree

of

**Master of Science**

at

The University of Waikato

by

Xu Zhang

The University of Waikato

2012

### **Abstract**

The Uninterrupted Power Supplies (UPSs) provide short term power back up to electrical loads when the mains power fail. Usually UPSs employ battery packs as the energy storage device. However the limitations of battery packs can affect the UPS performance.

As an alternative energy storage device, the supercapacitor (SC) technology is well developed over the past 30 years. Due to recent developments, single cell commercial supercapacitors are available up to about 5000 farads. Over the past 10 years, supercapacitor direct current (DC) voltage ratings have gradually increased to about 2.7 V/cell. New lithium based supercapacitor families have DC ratings up to 3.5 V/cell. For the high current applications, the supercapacitors have some advantages over batteries, which are the low effective series resistance (ESR), high power densities and high surge withstand capability.

This thesis is a continuation of the work begun by Kozhiparambil, P. K. on Surge Resistant Uninterrupted Power Supply (SRUPS). The reason for this continual research is due to identify weaknesses in original of SRUPS work with regard to the design of the charger. To reduce the components contain, also achieve common mode transient rejection capability, a flayback mode high current charger with power factor correction has been developed for charging the SC banks.

The prototype circuit includes multiple SC banks to transfer the energy from the 240 V, 50 Hz power line to the load maintaining high isolation level. The loads receive continuous and surge free power from the SC banks, and has electrical isolation from the main power line. An IGBT is used as a switch for the flyback charger, which has the advantage of high current capability.

The experimental results show the design was valid for the SRUPS and it demonstrated the capability to transfer the energy through a flyback charger with power factor correction.

## **Acknowledgements**

This thesis would not be able to be completed without the support and encouragement of others over two years of hard work.

I would like to express my gratitude and appreciation to my academic supervisor, Mr. Nihal Kularatna. Without his wisdom, guidance and insight I would not have been able to complete this thesis to the academic standard required. His time and contribution to the research has been immense and I will always be thankful.

This research follows on from the previous work started by Mr. Parthasaradhy Kumaran Kozhiparambil and I would like to thank him for his invaluable input at the beginning of this research.

On the technical side, the efforts of laboratory technicians, Mr. Stewart Finlay, Mr. Viking Zhou, and Mr. Pawan Shrestha, are most appreciated. Everything I needed in terms of components and equipment was no problem for them.

Of course I could not have got to this point without the love and financial support from my parents who have supported their son's overseas studies for an arduous seven years.

I could not finish without also thanking the special lady in my life, Carol. The time, patience, generosity and love she gave me while we were students together in New Zealand will always be cherished.

## **Table of Contents**

| ABSTRACT                                                 | i   |

|----------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                         | ii  |

| TABLE OF CONTENTS                                        | iii |

| LIST OF TABLES                                           | iv  |

| LIST OF FIGURES                                          | v   |

| NOMENCLATURE                                             | vi  |

| CHAPTER ONE: INTRODUCTION                                |     |

| 1.0 Introduction                                         | 3   |

| 1.1Introduction to uninterrupted power supply topologies | 3   |

| 1.1.1 Off-line topology                                  | 3   |

| 1.1.2 Hybrid topology                                    | 5   |

| 1.1.3 On-line topology                                   | 6   |

| 1.2 Research motivations                                 | 7   |

| 1.2.1 Supercapacitor energy storage capability           | 7   |

| 1.2.2 Surge protection                                   | 9   |

| 1.2.2.1 Conventional surge protection devices            | 9   |

| 1.2.2.2 Supercapacior surge withstand capability         | 10  |

1.3 Pervious research. 1.4 Development..... 12 1.5 Thesis arrangement. 13

### **CHAPTER TWO: BACKGROUND**

10

| 2.0 Background                                                                                                                                                                                                                                    | 17                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.1 Supercapacitors                                                                                                                                                                                                                               | 17                         |

| 2.11 Supercapacitor lifetime evaluation                                                                                                                                                                                                           | 17                         |

| 2.12 Reliability                                                                                                                                                                                                                                  | 23                         |

| 2.13 Energy and power                                                                                                                                                                                                                             | 24                         |

| 2.14 Balancing circuits                                                                                                                                                                                                                           | 26                         |

| 2.15 Modeling                                                                                                                                                                                                                                     | 28                         |

| 2.16 Surge withstand capability                                                                                                                                                                                                                   | 30                         |

| 2.2 Charge circuit                                                                                                                                                                                                                                | 32                         |

| 2.21 Flyback converter                                                                                                                                                                                                                            | 32                         |

| 2.22 Transformer design                                                                                                                                                                                                                           | 34                         |

| 2.23 Continuous and discontinuous mode                                                                                                                                                                                                            | 35                         |

| 2.24 Transformer equivalent circuit                                                                                                                                                                                                               | 36                         |

| 2.25 Energy losses in transformer windings                                                                                                                                                                                                        | 39                         |

| 2.251 Hysteresis losses                                                                                                                                                                                                                           | 39                         |

| 2.252 Eddy current losses                                                                                                                                                                                                                         | 40                         |

| 2.26 Proximity effect                                                                                                                                                                                                                             | 43                         |

| 2.27 Multiple layers                                                                                                                                                                                                                              | 43                         |

| <b>2 2 1 1</b>                                                                                                                                                                                                                                    | 43                         |

| 2.28 Litz wires                                                                                                                                                                                                                                   |                            |

| 2.28 Litz wires.         2.29 Snubbers.                                                                                                                                                                                                           | 46                         |

|                                                                                                                                                                                                                                                   | 46<br>46                   |

| 2.29 Snubbers                                                                                                                                                                                                                                     |                            |

| <ul><li>2.29 Snubbers.</li><li>2.291 Resistor-capacitor design.</li></ul>                                                                                                                                                                         | 46                         |

| <ul><li>2.29 Snubbers.</li><li>2.291 Resistor-capacitor design.</li><li>2.292 Resistor-capacitor-diode design.</li></ul>                                                                                                                          | 46<br>47                   |

| <ul> <li>2.29 Snubbers.</li> <li>2.291 Resistor-capacitor design.</li> <li>2.292 Resistor-capacitor-diode design.</li> <li>2.3 Power factor correction.</li> </ul>                                                                                | 46<br>47<br>50             |

| <ul> <li>2.29 Snubbers</li></ul>                                                                                                                                                                                                                  | 46<br>47<br>50<br>51       |

| <ul> <li>2.29 Snubbers.</li> <li>2.291 Resistor-capacitor design.</li> <li>2.292 Resistor-capacitor-diode design.</li> <li>2.3 Power factor correction.</li> <li>2.4 Insulated gate bipolar transistors.</li> <li>2.5 Surge waveforms.</li> </ul> | 46<br>47<br>50<br>51<br>53 |

### CHAPTER THREE: THE CIRCUIT DESCRIPTION

| 3.0 The circuit description.63 | ; |

|--------------------------------|---|

|--------------------------------|---|

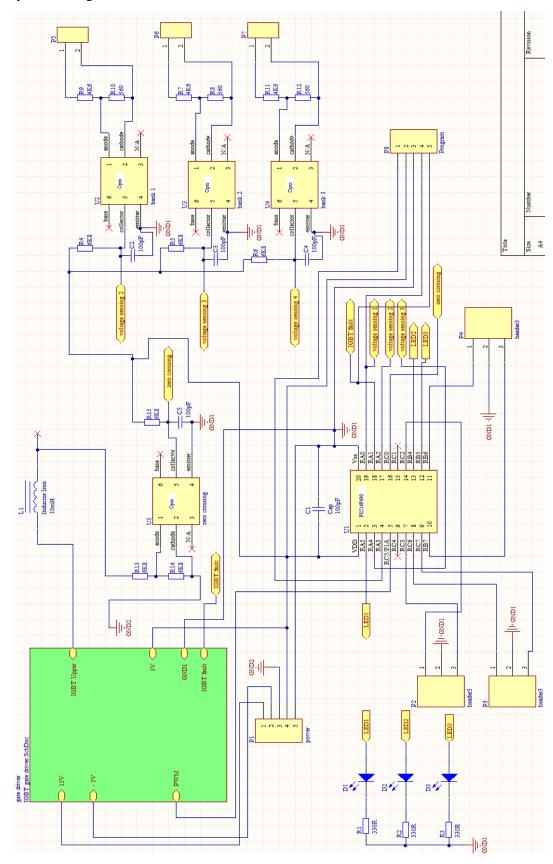

| 3.1 Overview of surge resistant uninterrupted power supply | 63 |

|------------------------------------------------------------|----|

| 3.2 Microcontroller                                        | 64 |

| 3.3 Transformer design                                     | 65 |

| 3.4 Insulated gate bipolar transistor driver               | 69 |

| 3.5 Flyback charger                                        | 72 |

| 3.6 Pulse-width modulation inverter                        | 73 |

| 3.7 The circuit control routines                           | 74 |

### **CHAPTER FOUR: RESULTS**

| 4.0 Results                                                | 79 |

|------------------------------------------------------------|----|

| 4.1 Insulated gate bipolar transistor driver testing       | 80 |

| 4.2 Flyback charger testing                                | 82 |

| 4.3 Switch circuit testing                                 | 85 |

| 4.4 Measurements summary for evaluating SRUPS performances | 86 |

### CHAPTER FIVE: CONCLUSION AND FUTURE DEVELOPMENT

| 5.0 Conclusion and future development | 91 |

|---------------------------------------|----|

| 5.1 Conclusion                        | 91 |

| 5.2 Future development                | 91 |

### APPENDICES

| 5                          |

|----------------------------|

| 5                          |

| 6                          |

| 7                          |

| 9                          |

| 9                          |

| 00                         |

| 01                         |

| 02                         |

| 03                         |

| 5<br>6<br>7<br>9<br>0<br>0 |

| REFERENCES   | 119 |

|--------------|-----|

| BIBLIOGRAPHY | 123 |

## **List of Tables**

| Table 2.1 The electrical characteristics of different supercapacitor families | 5    |

|-------------------------------------------------------------------------------|------|

|                                                                               | 26   |

| Table 2.2 A summary of test results applicable to the three supercapacitor    |      |

| families                                                                      | 30   |

| Table 2.3 Characteristics of IGBT, power MOSFETs, bipolars and darling        | tons |

|                                                                               | 53   |

| Table 3.1 The supercapacitor switching sequent in the condition of termin     | al   |

| voltages                                                                      | 64   |

## **List of Figures**

| Figure 1.1: Block diagram of off-line UPS                                      | 5        |

|--------------------------------------------------------------------------------|----------|

| Figure 1.2: An oscillograph of AC output during the transfer process           | s of an  |

| off-line UPS                                                                   | 5        |

| Figure 1.3: Block diagram of hybrid UPS                                        | 6        |

| Figure 1.4: Block diagram of on-line UPS                                       | 7        |

| Figure 1.4: Power densities and energy densities of various storage device     | es       |

|                                                                                | 8        |

| Figure 1.6: (a) the chemical structure of bidirectional breakover diode, (b    | o) BDD   |

| electronics symbol, (c) the V-I characteristics                                | 10       |

| Figure 1.7: The block diagram of SCs based surge free UPS                      | 11       |

| Figure 1.8 Block diagram of surge resistant UPS by inductive coupling          | 12       |

| Figure 2.1: The supercapacitor of BCAP350 with four thermocouples              | 18       |

| Figure 2.2: Energy cycling test with pulse period of 14 seconds                | 18       |

| Figure 2.3: Comparison between the core and ambient temperatures               | 19       |

| Figure 2.4: BACP350 core temperatures for different rated current              | 20       |

| Figure 2.5: Supercapacitor cylindrical structure                               | 21       |

| Figure 2.6: Variation of capacitance and ESR vs.log-lifetime                   | 24       |

| Figure 2.7: Evolution of symmetric Supercapacitor cell voltage, ener           | gy and   |

| power                                                                          | 25       |

| Figure 2.8: The schematic of passive balancing circuit                         | 27       |

| Figure 2.9: The schematic of active balancing circuit                          | 27       |

| Figure 2.10: The first order supercapacitor model                              | 28       |

| Figure 2.11: Advance equivalent circuit of a supercapacitor                    | 29       |

| Figure 2.12: Temperatures affect to the behavior of leakage current            | 39       |

| Figure 2.13: Waveforms shows voltage across Cap-xx (0.18F, 2.3V                | 7) after |

| repeated 6.6kV surges (a) uncharged supercapacitor, (b) with initial charge no |          |

| capacitor varying from 200mV to 1.8V                                           | 31       |

| Figure 2.14: the surges applied to the supercapacitor of Cap-0.18 F            | when it  |

| operated in the voltage cycling                                         | 32        |

|-------------------------------------------------------------------------|-----------|

| Figure 2.15: A flyback circuit                                          | 33        |

| Figure 2.16: Operational waveforms for the flyback circuit in discor    | tinuous   |

| mode                                                                    | 34        |

| Figure 2.17: A ferrite core with three windings                         | 35        |

| Figure 2.18: The waveforms of winding current in (a) discontinuous me   | ode and   |

| (b) continuous mode                                                     | 35        |

| Figure 2.19: Vector diagram of no-load current of ideal transformer     | 37        |

| Figure 2.20: A model for an ideal transformer                           | 38        |

| Figure 2.21: Hysteresis loops with different factors                    | 40        |

| Figure 2.22: Uniform current flows in a conductor at low frequency      | 41        |

| Figure 2.23: Eddy current at high frequency                             | 41        |

| Figure 2.24: Equivalent circuit of a conductor                          | 42        |

| Figure 2.25: Multiple layer windings                                    | 43        |

| Figure 2.26: The litz wire has larger surface area than a round solid w | vire, (a) |

| solid wire, (b) litz wire                                               | 45        |

| Figure 2.27: Snubber circuit using Resistor-Capacitor network           | 47        |

| Figure 2.28: Resistor-Capacitor-Diode snubber circuit                   | 48        |

| Figure 2.29 V-I characteristics of RCD snubber                          | 48        |

| Figure 2.30: The net losses versus snubber sizes                        | 49        |

| Figure 2.31: Comparison waveforms between RC snubber and RCD snub       | ber       |

|                                                                         | 50        |

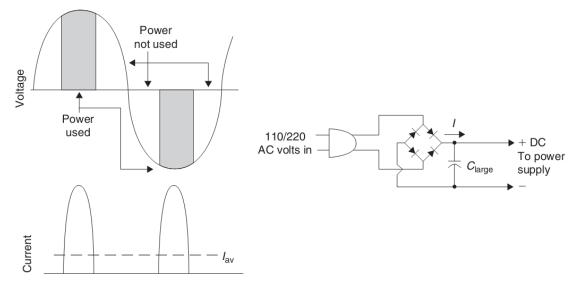

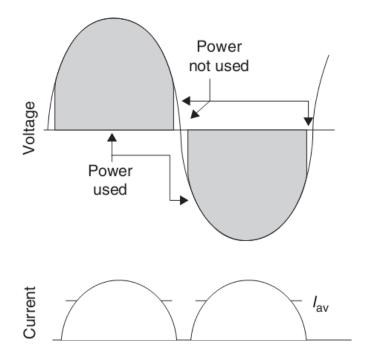

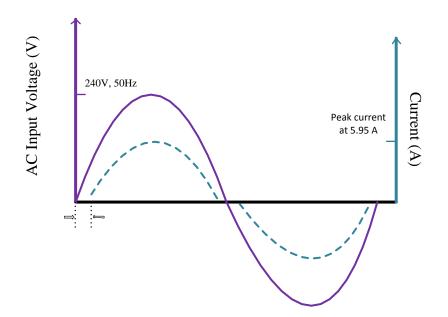

| Figure 2.32: The waveforms of a capacitive input filter                 | 51        |

| Figure 2.33: Power factor corrected input                               | 51        |

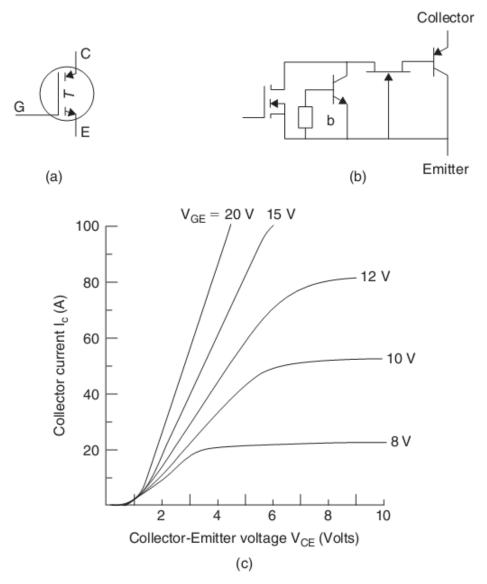

| Figure 2.34: IGBT (a) Symbol (b) Equivalent circuit (c) typical         | output    |

| characteristics                                                         | 52        |

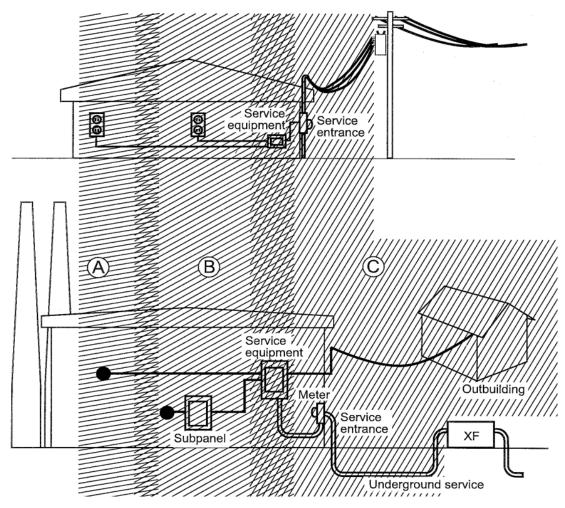

| Figure 2.35: Proposal of location categories A, B and C in Scenario I   | 54        |

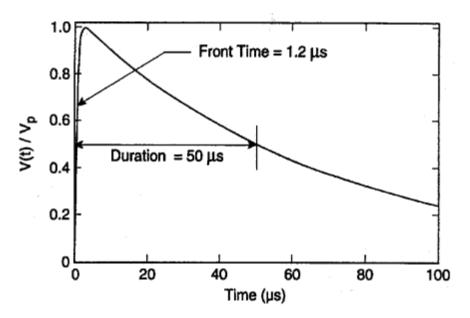

| Figure 2.36: Combination wave open-circuit voltage                      | 55        |

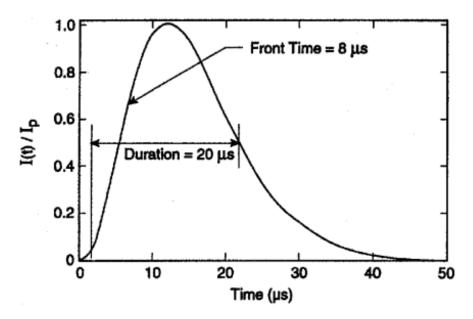

| Figure 2.37: Combination wave short-circuit current (Society, 2003)     | 56        |

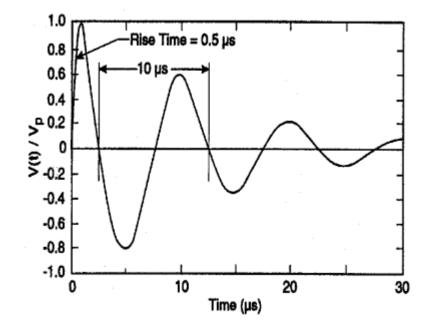

| Figure 2.38: 100 kHz ring waveform                                      | 57        |

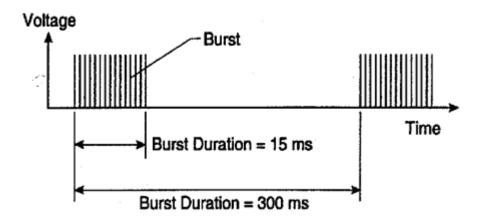

| Figure 2.39: The waveform of the EFT burst <b>xi</b>                    | 57        |

| A1                                                                      |           |

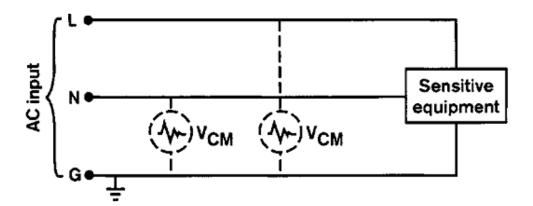

| Figure 2.40: Common mode (CM) noise                                          | 58        |

|------------------------------------------------------------------------------|-----------|

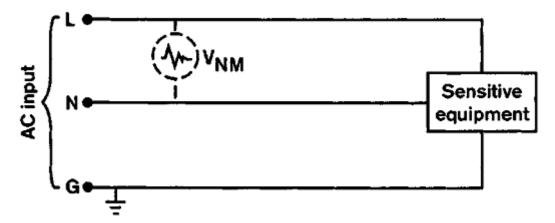

| Figure 2.41: Normal mode (NM) noise                                          | 58        |

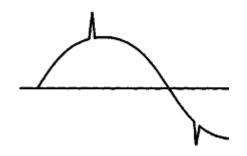

| Figure 2.42: Voltage spikes                                                  | 59        |

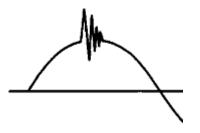

| Figure 2.43: Oscillatory decaying disturbances                               | 59        |

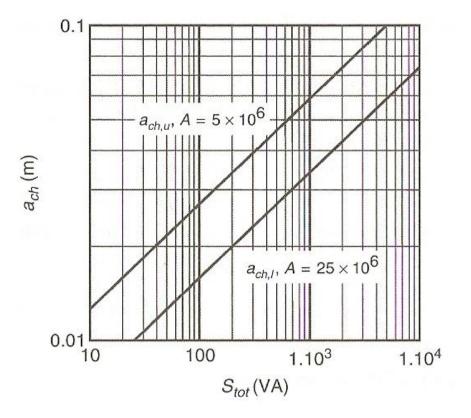

| Figure 3.1: Core size estimation for a non-saturated thermally limited       | d ferrite |

| core design                                                                  | 66        |

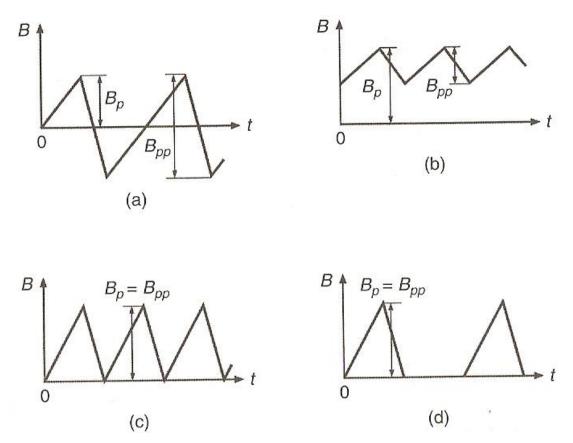

| Figure 3.2: Typical waveform and corresponding peak induction $B_P$          | 67        |

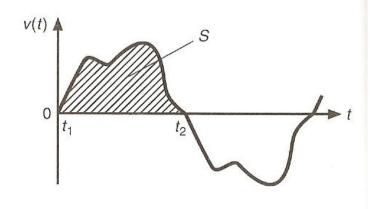

| Figure 3.3: The arbitrary voltage waveform across the transformer windin     | ng        |

|                                                                              | 69        |

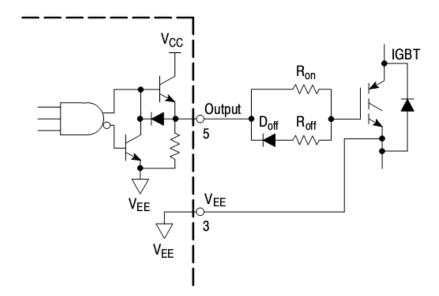

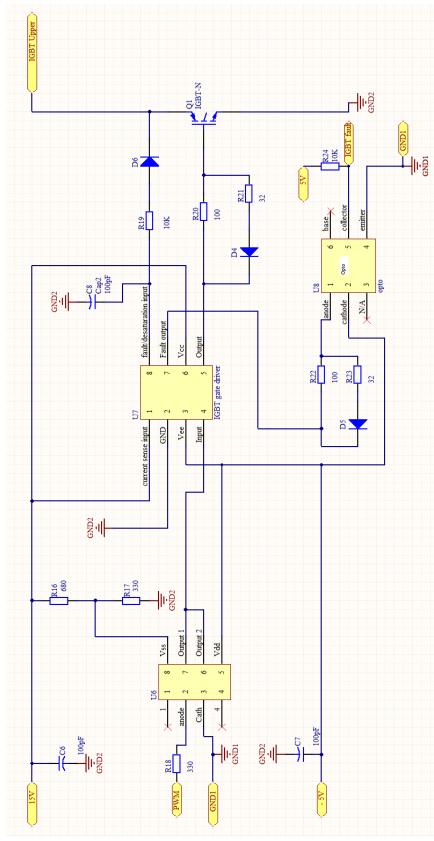

| Figure 3.4: Using a separate resistor for turn-on and turn-off               | 70        |

| Figure 3.5: The gate diver is negative triggered and offer a positive/r      | negative  |

| drive                                                                        | 71        |

| Figure 3.6: Desaturation circuit with support components                     | 72        |

| Figure 3.7: The block diagram of charge circuit                              | 73        |

| Figure 3.8: The flow chart of the supercapacitor based on-line UPS initia    | alization |

| routine                                                                      | 75        |

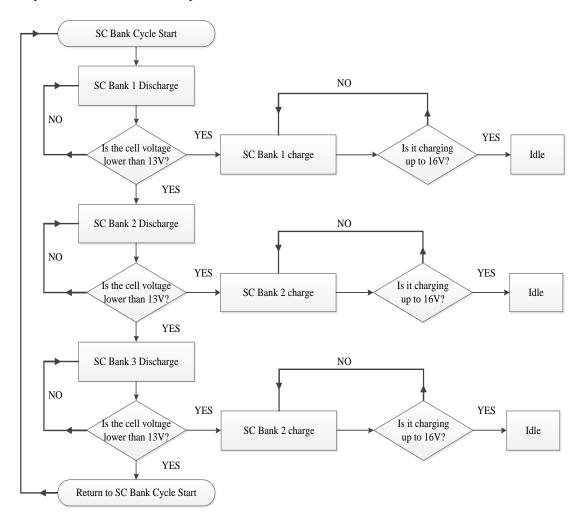

| Figure 3.9: The flow chart of supercapacitor banks switching routine         | 76        |

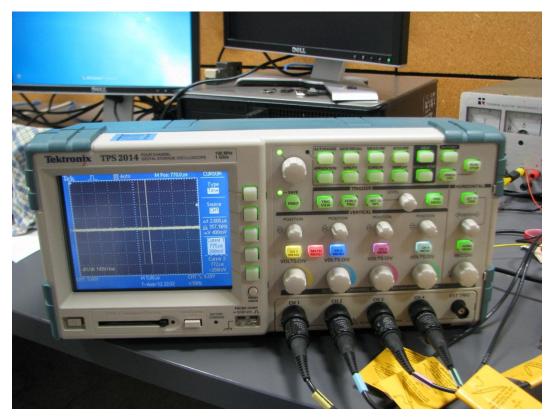

| Figure 4.1: Tektronix TPS 2024 digital oscilloscope                          | 80        |

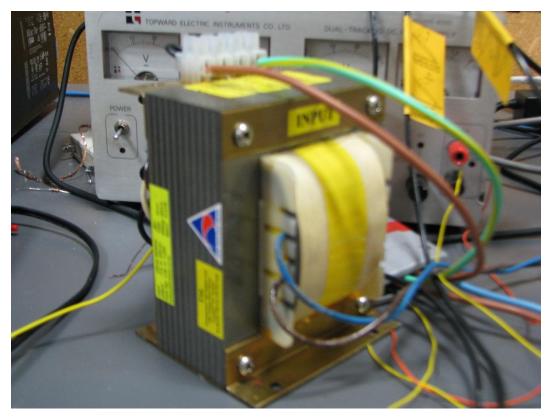

| Figure 4.2: Isolation transformer                                            | 80        |

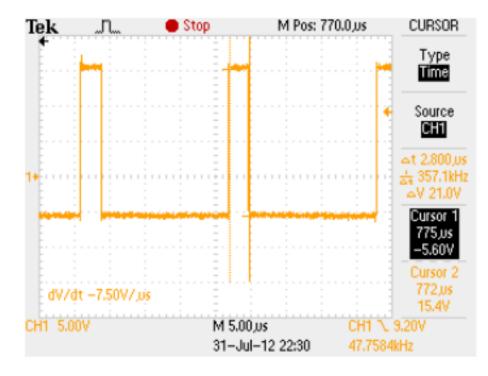

| Figure 4.3: The open circuit of PWM drive supplied by the IGBT driver        | 81        |

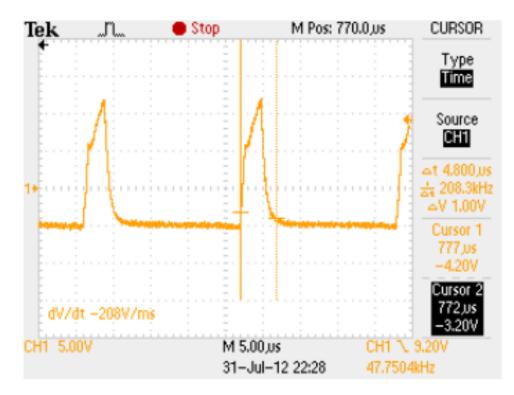

| Figure 4.4: Actual waveforms of PWM output                                   | 82        |

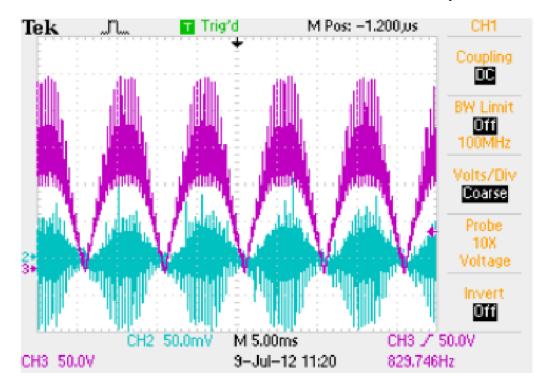

| Figure 4.5: The voltage (purple) and current (blue) waveforms of the         |           |

| transformer primary winding                                                  | 83        |

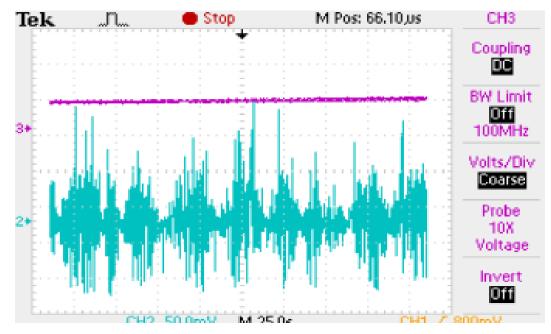

| Figure 4.6: The voltage (purple) and current (blue) waveforms of the         |           |

| transformer secondary winding                                                | 83        |

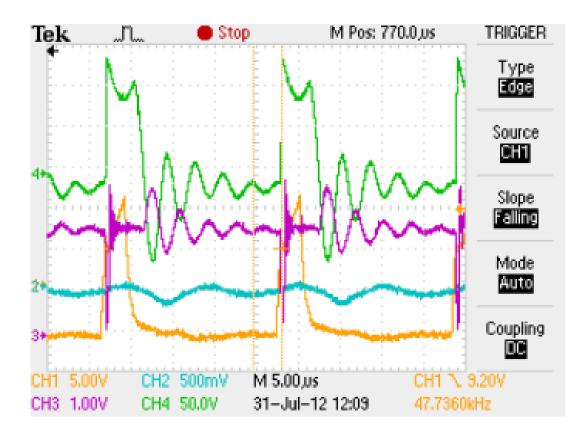

| Figure 4.7: Flyback charger waveforms                                        | 84        |

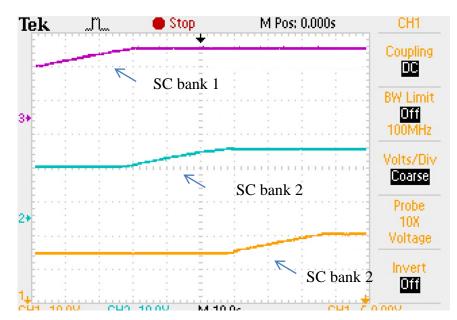

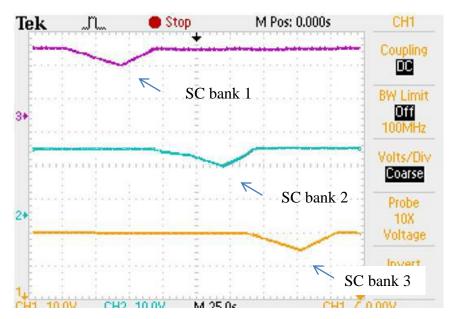

| Figure 4.8: Charge the SC banks individually in the start-up mode            | 85        |

| Figure 4.9: Switching the SC banks in a cycling mode during normal operation |           |

|                                                                              | 86        |

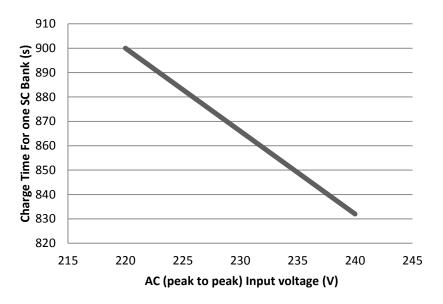

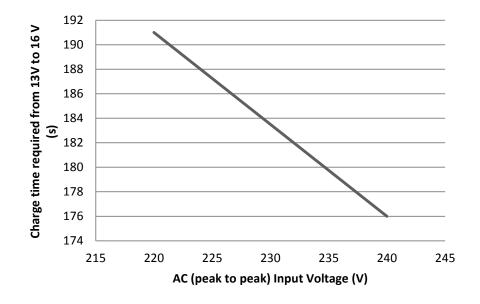

| Figure 4.10: Charge time is differ with voltage source                       | 86        |

| Figure 4.11: The charge time required for cycling operation                  | 87        |

## **Nomenclature**

| AC     | Altering Current                                  |

|--------|---------------------------------------------------|

| ADC    | Analogue Digital Converter                        |

| BDD    | Bidirectional Breakover Diode                     |

| BJT    | Bipolar Junction Transistor                       |

| DC     | Direct Current                                    |

| EFT    | Electrical Fast Transient                         |

| ESR    | Effective Series Resistance                       |

| IEEE   | Institute of Electrical and Electronics Engineers |

| IGBT   | Insulated Gate Bipolar Transistor                 |

| LED    | Light Emitting Diode                              |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| MOV    | Metal Oxide Varistor                              |

| РСВ    | Printed Circuit Board                             |

| PIC®   | Peripheral Interface Controller                   |

| PWM    | Pulse Width Modulation                            |

| RC     | Resistance Capacitor                              |

| RCD    | Resistance Capacitor Diode                        |

| RMS    | Root Mean Square                                  |

| SC     | Supercapacitor                                    |

| SOA    | Safe Operating Area                               |

| SRUPS  | Surge Resistance Uninterrupted Power Supply       |

| UPS    | Uninterrupted Power Supply                        |

|        |                                                   |

# **Chapter One**

Introduction

### 1.0 Introduction

### 1.1 Introduction to uninterrupted power supply topologies

Business, industry and telecommunication use millions of electrical equipment. They provide control, data processing and communicating systems, which makes the term computer-integrated factory or computer-integrated business happen. For those systems to operate continuously without unexpected interruption, a reliable AC power supply is required.

To control the risk of power interruption, the uninterrupted power supply (UPS) was invented to be the emergency power source that provides the backup power supply to the equipment when the power source, typically the main power source, fails. The first commercial UPS system was invented in the 1950's, which was basic version involving rotating electrical machinery. After years of development, the rotating machinery components in the earlier version of UPS system were replaced by the electrical components. Therefore the physical size of UPS has been decreased, in turn decreasing the cost to approximately \$1 per watt (*PQ Assurance Journal*).

By the 1990s, UPS usage had expanded to cover not only industrial systems, but also residential systems. The statistics in 1992 show that three-phase large UPS system only occupied 37% of the UPS market (Katzaro,1993). Comparatively the single-phase system contributed almost two thirds of the UPS market. At this time the electrical transient interference is a major issue in the AC power line, which happens more frequently than a power fail. Therefore, the UPS designs were extended to provide surge protection for occurrences such as surging, transient, and lightning.

Presently, the commercial UPS systems are divided into three basic topologies, off-line, hybrid, and on-line types respectively.

1.1.1Off-line topology

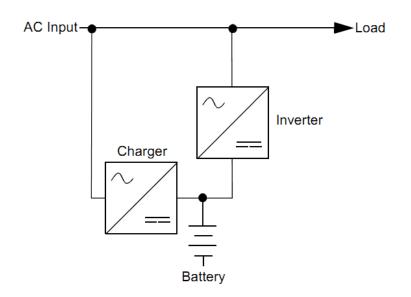

The block diagram of off-line UPS shows in Figure 1.1. The battery takes a charge through the converter, and holds the energy for power backup. In the normal operation, the load is powered directly from the AC power line, the filter on the AC power line provides a basic voltage filtering against the low energy interferences. In the event of power failure, the switch transfers to the standby power source, where the battery will carry the major load current.

The off-line UPS system is usually found in the domestic environment. It is cheap, easy to maintain, and a smaller in size and weight. The off-line UPS presents very low losses during the normal operation, because the battery and inverter normally off and physically disconnected from the power source. The power source carries the most of load current, only small amount charging current goes to the battery against the battery leakage. Therefore regardless of the battery leakage, the power loss on the off-line UPS during the normal operation is approximately zero.

The disadvantage of this type of UPS is response latency and low level surge protection. The transfer time is determined by the sum of detection time and switch transfer. When the AC power fails, an occurrence of voltage glitch is due to transfer time. The quality of line filter and surge suppression available in the off-line UPS are price dependent and may be absent in the low end version which makes them highly unreliable when operated in the environment of high level surge and transient.

When a power failure occurs presenting in Figure 1.2, the off-line UPS switches to the inverter mode and operates in this mode until the main power is recovered again. The system switches from one mode to the other mode in the shortest possible duration, in order to supply uninterrupted power to the load. However the waveform at the middle of Figure 1.2 shows that the sine waveform goes flat, which means the main AC power fails. After a while, this power failure is detected and the inverter starts to operate for providing power to the load. This flat time is significantly demonstrated the response latency during the system switches from one operation mode to the other. The inverter output demonstrates in Figure 1.2 is not smooth sine waveform, contains voltage spikes, brownouts and blackouts. Those influences affect the performance of electrical load that connect to this

inverter, also may damage the electrical load which is sensitive to these voltage interferences.

Figure 1.1 Block diagram of off-line UPS (Khare & Kamil, 2009)

Figure 1.2: An oscillograph of AC output during the transfer process of an off-line UPS (Kularatna, 1998)

### 1.1.2 Hybrid topology

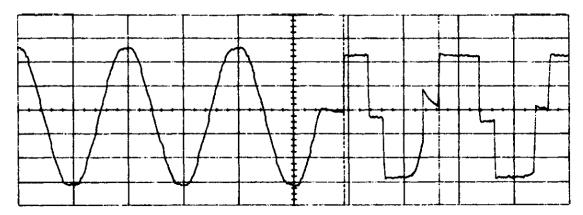

Principally, the hybrid UPS is developed from the off-line UPS. The transfer switch is replaced by a special saturated transformer that has three windings, two bifilar wind primaries and a secondary. The inductive coupling has the advantage of energy storage and faster transfer. However, this type of UPS is large, heavy, and has high thermal losses due to the local heating of the transformer. Figure 1.3

#### Chapter One: Introduction

shows the block diagram of the hybrid UPS.

Figure 1.3: Block diagram of hybrid UPS (Kozhiparambil, 2011)

### 1.1.3 On-line UPS topology

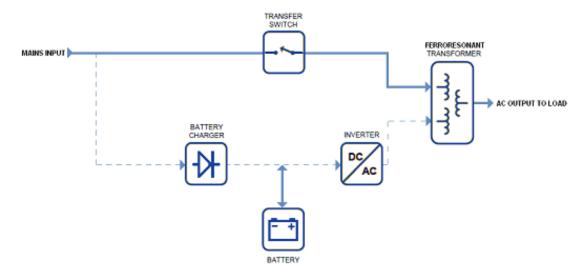

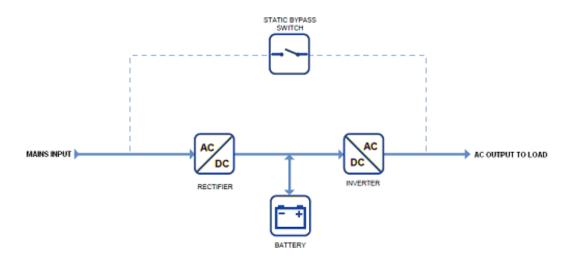

The on-line UPS system is designed for the equipment that operates in the "noisy" environment, or is sensitive to power fluctuation. The block diagram shows in Figure 1.4 the output after the rectifier and inverter is completely isolated from the main AC power source. The rectifier and inverter are always operating, which protect against surges, sags, spikes and transients. The AC input via the rectifier is stepped down to charge the battery, and the inverter boosts the battery power which is then fed into the load. When the main AC power fails, the rectifier simply drops out, and batteries then discharge to the load. When the power resumes, the rectifier carries the most loaded current and batteries start to charge and standby. In the normal operation, the batteries take a small amount of charging current against the self-discharge. The switch free circuit and on-line protection provide the fastest response time and high surge suppression level. However, it has the most complex design, requires a limitation of the charging current to prevent the rectifier from overcurrent, and a cooling system is required for batteries, in order to extend the battery lifetime.

### 1.2 Research motivation

Three UPS topologies were introduced in the previous section, which were designed to minimize the risk of power fail and surge damage. The circuit devolved from the direct connection to the inductive coupling, and the off-line protection to the on-line protection using a similar battery pack as an energy storage device. The battery is economic and highly reliable, but it has some drawbacks, such as:

- Limitation of the peak charge and discharging current.

- The overcurrent can lead to boiling chemicals that will short or terminate battery service life.

- Rush incoming current may damage the battery.

This research investigates the possibility of using the supercapacitor to be an alternative energy storage device for on-line UPS system, as well as utilizing the supercapacitor surge sustainability to simplify the UPS surge protection design.

1.2.1 Supercapacitor energy storage capability

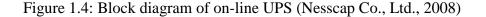

The supercapacitors are also known as the ultracapacitor. The supercapacitors

(SCs) are high efficient energy storage device that has higher instantaneous power densities than conventional batteries, and higher energy densities than the electrostatic capacitors as depicted in Figure 1.5. The supercapacitors are a non-chemical reaction device, where the energy is stored via an electrostatic process. It allows the supercapacitor to charge and discharge at high rate of current, making it possible to be used as a high current source for the power applications.

Figure 1.5: Power densities and energy densities of various storage devices (Kozhiparambil, 2011)

The Maxwell Technology proposed approach of a SC module consists of two parallel capacitor packs, where each pack contains 140 cells connecting in series. The SC module is designed to drive a hybrid bus that weighs 9600 kg plus 5400 kg for the passenger mass, which must be satisfied in both conditions of long distance service and fast acceleration. According to the experiment results, the capacitor module in the long term service process presents the utility of high energy storage, which is able to supply over 178kWh. On the other hand, the acceleration experiment required to accelerate from zero speed to 25mph is 295Wh, which demonstrated the capacitor model has the advantage of high peak output current (Miller, 2011) [8]. Therefore, this study will discuss the possibility of the supercapacitor bank as an alternative energy storage device for the on-line

UPS.

### 1.2.2 Surge protection

1.2.2.1 Conventional surge protection devices

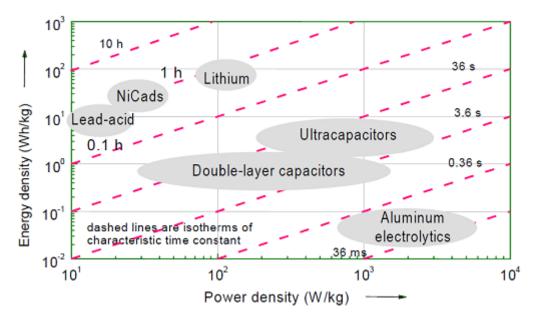

The metal oxide variators (MOV) and bidirectional breakover diodes (BBD) are the most common electrical surge suppression devices, providing a basic surge protection. These devices have the advantages of low cost and simple structure. However those component are limited on the response time, maximum clamping voltage and repeated pulse current sustainability.

MOVs are nonlinear voltage dependent devices which have an electrical behavior similar to back-to-back zener diodes. It is often used to guard against excessive voltage transients. The devices could conduct heavily when a short duration high voltage transits occurs, and provide a current path to absorb transients energy.

Bidirectional breakover diodes (BDD) consist of two avalanche diodes, which can be switched from the non-conduct state to the conduct state for either polarity of applied voltage. The Figure 1.6 shows the chemical structure, electronics symbol and V-I characteristics. In the non-conduct state, a very small amount of leakage current is exhibited in either direction. The conduction is occurred when the breakover voltage is reached in either polarity across the two terminals. The Bidirectional breakover diode is often used in the high voltage protection circuit, which requires a protection against transients in either positive or negative.

Figure 1.6: (a) the chemical structure of a BDD, (b) BDD electronics symbol, (c) the V-I characteristics ( Khanchandani, K. B. & Singh, M. D, 2008)

The major drawback to those two protection devices is, during the shunt period, the occurrence of breakdown causes localized heating. If the heat generation is excessive, the device may melt, burn, vaporize or be otherwise damaged.

### 1.2.2.2 Supercapacitor surge withstand capability

The journal article published by Nihal Kularatna and his team (Kularatna, Fernando, Pandey, & James, 2011), demonstrated the supercapacitor surge sustainability by testing different commercial brands of supercapacitor families. The result demonstrated that the Cap 0.18F supercapacitor could easily withstand over 200 hits of 6.6 kV repeated surges before the occurrence of failure. Another test sample, Maxwell Boostcap 230F exhibited robust surge sustainability, 600 repeated surges (6.6 kV) could not damage it. Therefore, the test results have allowed others to expend their work, to develop applications of surge protection utilizing the property of supercapacitor surge sustainability.

### 1.3 Previous research

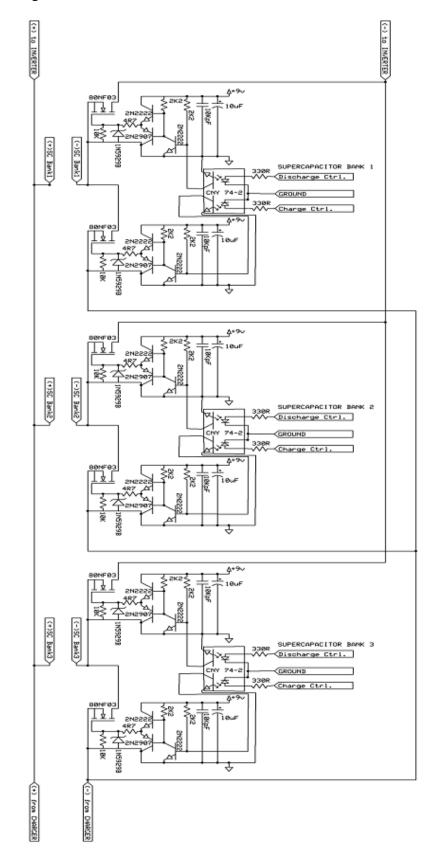

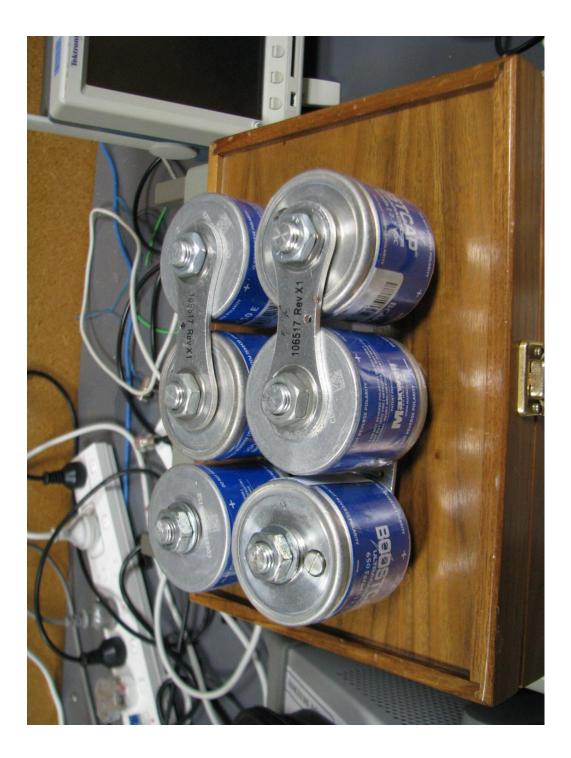

The master engineering student Kozhiparambil P. K. who proposed an approach

of supercapacitor based surge free on-line UPS. The core concept is that three supercapacitor banks operate independently as energy transfer devices. The capacitor banks provide a complete isolation to the load, and absorb the transients to protect the load from damage. The sizing of the capacitor bank is considered by taking into account their system parameters and properties, such as duty cycle, efficiency, cost, etc.

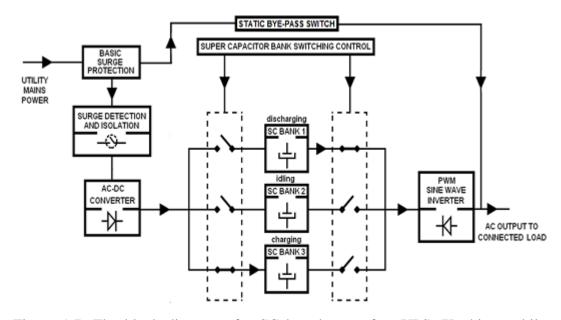

Figure 1.7 depicts the operation of dynamic supercapacitor banks (SC bank). In normal operation, one of the SC banks, for example SC bank 3, gets charge from the AC power line. Meanwhile, the SC bank 1 operates in the discharge mode. It releases its energy to the inverter, and will return to the charge mode when the terminal voltage is lower than the inverter requirement. The SC bank 2 is kept the full charge and standby, and will replace the SC bank 1 before it disconnects from the inverter. Therefore the SC banks are cycling. If assuming the average rate of charge (from the utility power line) is greater than the rate of discharge (to the inverter), then the inverter is powered by the SC banks and completely isolated from the utility power line. Therefore the surges at any given operation modes have no chance to affect the load.

Figure 1.7: The block diagram of a SC based surge free UPS (Kozhiparambil, 2011)

### 1.4 Development

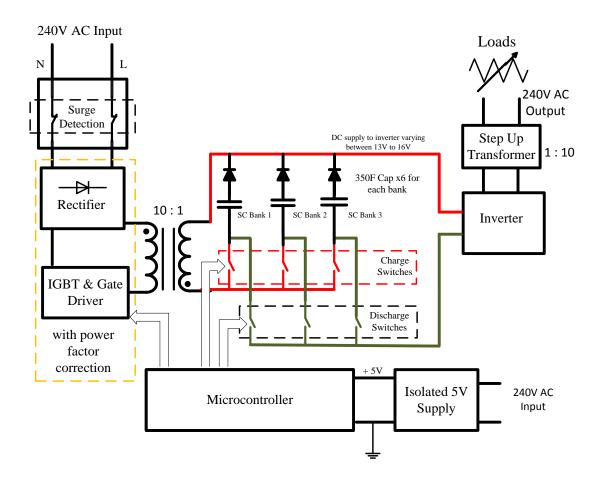

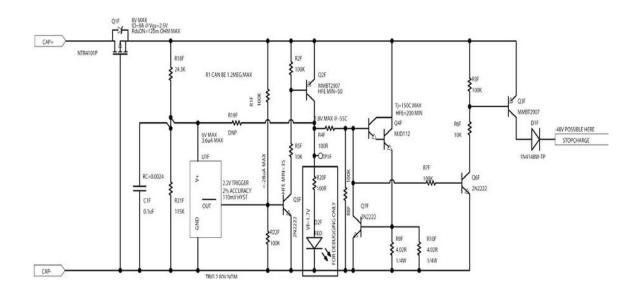

The UPS approach offered by Kozhiparambil P. K is used a cycling of SC banks to separate the load from the main power, in order to avoid the surge damages. However the charge circuit in this approach is very complicated. Some components are easily damaged by the repeated surges. So the charger could be failed due to component failure. To overcome this problem, this research proposes a technique that employs a flyback type transformer to replace entire charge circuit. It is aimed to develop a simple and reliable charge circuit for charging supercapacitor banks. The new charger must able to supply high rate of charging current with high efficiency, and withstand all level surges that standard is defined by IEEE C62.40. The new proposal of supercapacitor surge free on-line UPS is depicted in Figure 1.8.

Figure 1.8: Block diagram of a surge resistant UPS with inductive coupling

The switch attached on the primary winding of transformer is switching at certain frequency. The primary winding gats charge during the switch on-period, and then release the energy to the secondary when switch is in off period. The supercapacitor banks connect to the secondary wind gets charge through the weak coupling. The energy transfer via the magnetic coupling makes it possible that the electrical isolation exists between AC main line and the load. The supercapacitor banks are only exposed to transients that propagate through the magnetic coupling. The supercapacitor has the advantage that it is capable of absorbing the surges. The propagation of surges and transients should absorb and vanish at the stage of supercapacitor banks, in order to protect other electrical components on the inverter side. Irrespective of the operation mode, the load has no chance to create a loop for transients in the energy transfer process. Hence the transfer of energy takes place in complete isolation with protection against common-mode transients. Because the valid inverter input voltage is between 12 V to 20 V. Therefore, the supercapacitor banks are design to charge and discharge in a voltage window between 13 V to 16 V.

### 1.5 Thesis arrangement

Chapter One : Introduction. Introduce to the fundamental of three UPS topologies off-line, hybrid and on-line, which are usually used in the commercial UPS system. Then briefly discuss the advantages and disadvantages of the three UPS topologies, and address the reason why we investigate in the new topology of supercapacitor based UPS.

Chapter Two : Background. It is summering the essential components and their relevant characteristics required for the design project.

Chapter Three : Circuit Description. It discusses the actual circuit and control routines. The procedure of the circuit developing is demonstrated in one step by one step.

Chapter Four : Experiment results. It discusses the measurements and results that can be used to evaluate the performance of project.

Chapter Five: Conclusion and Future Development. It concludes the achievements that have been done in this research, and recommend the future development for a better design approach.

# **Chapter Two**

Background

#### 2.0 Background

#### 2.1 Supercapacitors

Supercapacitor families based on electric double layer effect have entered into a mature stage for usage in many applications, such as electric vehicles, UPS systems, battery-supercapacitor hybrids and cellular phones. The following section will discuss the characteristics of supercapacitor from the different aspects.

## 2.11 Supercapacitor lifetime evaluation

The lifetime of a supercapacitor is of considerable industrial interest. An investigation by Maxwell discovered that the electrical and thermal stresses are mainly affected by their aging characterization. Two different methods were designed to test the lifetime of the supercapacitor. The first method is power cycling where the devices charge up to rated voltage beginning at zero volts, then discharge from the rated voltage to half rated voltage, and then repeat this process continuously. The second method is where the unit holds the constant voltage and temperature stress.

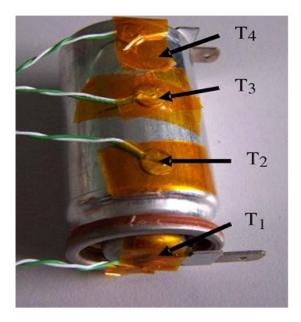

The references (Kötz, Hahn, & Gallay, 2006) and (Gualous, Louahlia-Gualous, Gallay, & Miraoui, 2009) describe an experiment using a Maxwell BACP350 supercapacitor, which is rated for 2.5 V. The experiment setup consists of four thermocouples that were surface mounted on the body of the supercapacitor as depicted in demonstration mode in Figure 2.1.

Figure 2.1: The supercapacitor of BCAP350 with four thermocouples (Gualous et al., 2009)

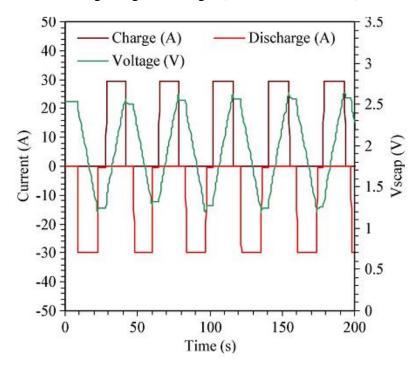

Figure 2.2 graphically demonstrates an energy cycling experiment, where supercapacitors charge and discharge with a quasi-square wave of current. Consequently, the terminal voltage sweeps between its rated voltage (2.5 V) and half rated voltage (1.25 V). The voltage cycling is designed within this voltage window because they can store and provide approximately 75% of its maximum energy, without creating design challenge. (Gualous et al., 2009)

Figure 2.2: Energy cycling test with pulse period of 14 seconds (Gualous et al.,

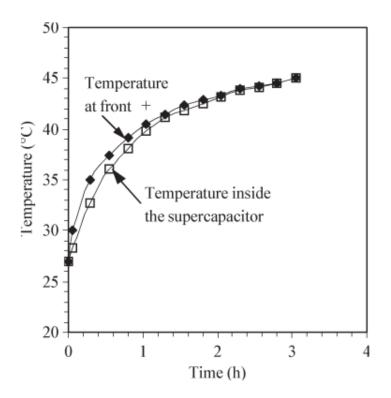

Figure 2.3 shows the thermal stresses of the energy cycling experiment. The supercapacitors will get charged and discharged at high current rate, while the temperature increases over time. In the cycling operation, the cell core temperature rises approximately 2°C more than the ambient temperature. In the steady state (holding the voltage constantly), the core temperature appears 1°C above the ambient temperature. The small temperature difference makes it evident that the supercapacitor has very low thermal resistance, making it suitable for high power transfer because of lower thermal losses and body heating.

Figure 2.3: Comparison between the core and ambient temperatures (Gualous et al., 2009)

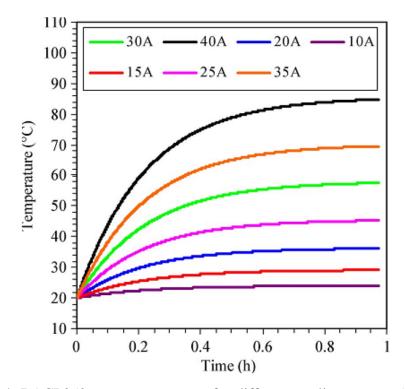

The rate of charging/discharging current is another important parameter to affect thermal drop out behavior. A comparison graph of temperature increases due to the difference of cycling current as depicted in Figure 2.4, illustrates the increasing core temperatures over one hour period. As the results show, in high power applications, a heat sink is necessary, and the design should be based on the rate of charging/discharging current.

Figure 2.4: BACP350 core temperatures for different cycling current (Gualous et al., 2009)

Although the supercapacitor has very low thermal resistance, for some high current application, it is still a major consideration. A numerical thermal model demonstrated in the flowing section was built by Hamid Gualous, which helps to understand the thermal behavior comprehensively (Gualous et al., 2009). The distribution of heat inside the supercapacitor spreads from the high temperature zone to another zone where the temperature is lower. The heat transformation can be expressed as

$$\nabla^2 T + \frac{P}{\lambda} = \frac{\rho C_p}{\lambda} \frac{\partial T}{\partial t}$$

(2.1)

(Gualous et al., 2009)

Where :

- $V^2$  is the Laplacian operator.

- $\rho$  is the density of capacitor.

- $\lambda$  is the supercapacitor thermal conductivity

- $C_p$  is the heat-specific capacity.

# • *P* is the local volumetric density.

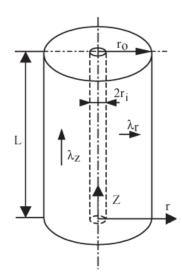

The physical structure of the supercapacitor can be described as a cylindrical tube, as shown in Figure 2.5. The heat transformation inside this supercapacitor is assumed to be axis-symmetrical, and the heat conduction equation is used in two directions, i.e., in the radial and the axial direction. The conductivity along axial and radial directions are set to be  $\lambda z$  and  $\lambda r$  respectively, and the physical model is given by

$$\rho C_p \frac{\partial T(r, z, t)}{\partial t} = \lambda_r \frac{\partial^2 T(r, z, t)}{\partial r^2} + \frac{\lambda_r}{r} \frac{\partial T(r, z, t)}{\partial r} + \lambda_z \frac{\partial^2 T(r, z, t)}{\partial z^2} + P$$

(2.2)

(Gualous et al., 2009)

where:

- $r_i < r < r_o, 0 \le z \le L$ , and  $0 < t \le t_f$

- r is the radial coordinate, z is the axial coordinate and

- $r_i$  and  $r_o$  are the internal and external radii of the supercapacitor.

Figure 2.5: Supercapacitor cylindrical structure (Gualous et al., 2009)

The supercapacitor consists of many layers. The thermal resistance in the signal

Chapter Two: Background

layer can be written as

$$R_{\rm th} = \frac{\ln(r_o/r_i)}{2\pi\lambda L}.$$

(2.3)

(Gualous et al., 2009)

However for the multiple-layer supercapacitor, each layer has a different radius; the equivalent thermal resistance along the radial direction is the sum of all the layers. For example, for a four-layer structure, the equation can be written as

$$R_{\rm th} = \frac{1}{2\pi\lambda_c L} \ln\left(\frac{r_i + e_c}{r_i}\right) + \frac{1}{2\pi\lambda_s L} \ln\left(\frac{r_i + 2e_c + e_a + e_s}{r_i + 2e_c + e_a}\right) + \frac{l}{2\pi\lambda_c L} \ln\left(\frac{r_i + 2e_c + e_a}{r_i + e_c + e_a}\right) + \frac{1}{2\pi\lambda_a L} \ln\left(\frac{r_i + e_c + e_a}{r_i + e_c}\right)$$

$$(2.4)$$

(Gualous et al., 2009)

where :

- e c is the thickness of active carbon.

- e s is the thickness of separator.

- e a is the thickness of aluminium.

- $\lambda c$  is the active carbon thermal conductivity

- $\lambda$  a is the aluminium thermal conductivity

- $\lambda$  s is the separator thermal conductivity

Along the axial direction, the thermal conductivity of all the layers is assumed to be the same as the aluminum conductivity. Hence they form a parallel thermal resistance. The expression for the parallel thermal resistance is

$$\frac{1}{R_{\rm th}} = \sum_{n=1}^{N} \frac{1}{R_{\rm th,n}}$$

(2.5)

(Gualous et al., 2009)

where n is the number of the layer and N is total number of layers. In fact the conductivity of the carbon and the separator is much lower than the conductivity of aluminium. The equation can be simplified, depending only on the conductivity of aluminium.

### 2.12 Reliability

Reliability and service life are very important considerations when designing commercial applications. The reliability is the subject that relates to the quality of products, which is defined as:

"The probability that a product performs its intended function without failure under specified condition for a specified period of time. The definition contains three important elements: intended function, specified a period of time, and specified conditions." (Albertsen, 2010)

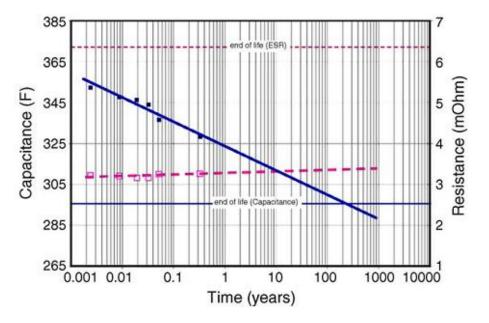

For determining the failure of the supercapacitors, an experiment was developed by R. Kötz and his team, where the supercapacitor held at 2.5 V at room temperature. The result as depicted in Figure 2.6 shows, the occurrences of an increase of ESR and reduction of capacitance are during in the server time. On the other hand, the temperature variation is also effect the aging process, which is also discussed by the R. Kötz. An increase of the temperature of 10°C will result in an accelerated aging factor between 1.7 and 2.5. For more information, please refer to the reference of.

Figure 2.6: Variation of capacitance and ESR versus lifetime (Kötz et al., 2006)

# 2.13 Energy and Power

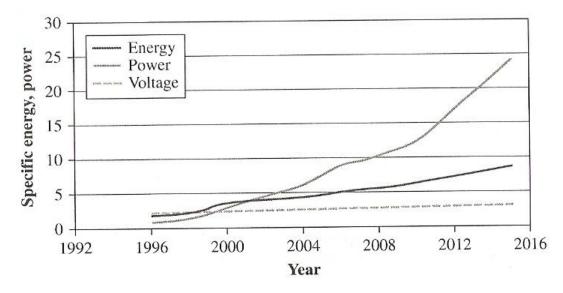

Figure 2.7 shows a great development of supercapacitor on the cell voltage, energy storage capability and power supply capability. Because this development, many applications are developed to use supercapacitors as alternative energy storage devices. For general purpose, all the data sheets list the cell mass and dimensions that can be used to calculate energy density. As a voltage device, it evaluates on two aspects, which are specific energy (*SE* in j/kg, Wh/kg) and energy density (*ED* in j/L, Wh/L) respectively, and where cell mass (*E*) and dimensions (*L*) are used to calculate volume. The expressions are given

$$SE = \frac{CU_{mx}^2}{2M} (J/kg) = \frac{CU_{mx}^2}{7200M} (Wh/kg)$$

(2.6)

(Miller, 2011)

(2.6)

$$ED = \frac{CU_{mx}^2}{2Vol} (J/L) = \frac{CU_{mx}^2}{7200Vol} (Wh/L)$$

(2.7) (Miller, 2011)

24

Figure 2.7: Evolution of symmetric supercapacitor cell voltage, energy and power (Miller, 2011)

The power performance of the supercapacitor is also important. Many applications require a high performance instantaneous power supply where the supercapacitor can be used. The most commonly used metric for power is matched load power,  $P_{ML}$ , and corresponding specific power defined as 2.9 and 2.10. The table 2.1 highlights the equivalent series resistance (ESR) with different commercial brands. The low ESR is the advantage for high power supply capability, and minor losses during the energy cycling process.

$$P_{ML} = \frac{U_{mx}^2}{4ESR_{dc}}$$

(2.8) (Miller, 2011)

$$SP_{ML} = \frac{U_{mx}^2}{4(ESR_{dc})M}$$

(2.9) (Miller, 2011)

| Parameters<br>as per data sheets | Cap-XX               | Nesscap                 | Maxwell Boostcap |

|----------------------------------|----------------------|-------------------------|------------------|

| Capacitance                      | 0.18 F               | 90 F                    | 230 F            |

| Rated DC Voltage                 | 2.3 V                | 2.7 V                   | 2.5 V            |

| Effective Series<br>Resistance   | $45\mathrm{m}\Omega$ | $0.33 \mathrm{m}\Omega$ | 2.2 mΩ           |

| Operating<br>Temperature Range   | -40 - 70 °C          | -40 - 65 °C             | -40 - 70 °C      |

| Leakage Current                  | 3.5 μΑ               | 0.75 mA                 | 0.45 mA          |

Table 2.1 The electrical characteristics of different supercapacitor families (Kularatna et al., 2011)

## 2.14 Balancing circuits

A supercapacitor module consists of many identical cells, and connecting them in series gives higher net output voltage. In the charging process, voltage distribution in the supercapacitor module is initially a function of capacitance. After a period of time, where each identical cell holds at a particular voltage level, this voltage distribution becomes a function of internal parallel resistance, which represents a leakage current.

A balancing circuit is required to equalize voltages on each identity cell. Without the voltage balancing, the cell voltages during the charging process, where the cell with smaller capacitances will be saturated and tend to overcharge, while the cell with greater capacitances will be charged to lower voltages.

When the capacitor module holds voltages in the steady state, a leakage current is present. The voltages decaying due to leakage current is a function of different resistances, which also cause unequaled cell voltages. The cell voltages discharge in higher rate, which should have lower leakage resistance, and vice versa.

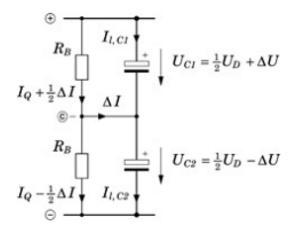

To overcome the problem discussed above, a balancing circuit is developed, and its schematic is demonstrated in Figure 2.8. It employs bypass resistances to balance terminal voltages of each individual cell, as well as compensation for variation in leakage current. The bypass resistance technology is called passive balancing. It only suits the low duty cycle applications. For the high duty cycle applications, Maxwell Technology recommends an active balancing circuit as depicted in Figure 2.9. It has advantages of performing in a wide temperature range and does compensate while in operation. Because of its fast response, it can be used in high frequency applications.

Figure 2.8: The schematic of passive balancing circuit (Ertl, Wiesinger, & Kolar, 2008)

Figure 2.9: The schematic of active balancing circuit (*Maxwell Technology*)

2.15 Modelling

Computer aided modelling is a term for a mathematical model, for simulating circuitry performance under laboratory circumstances. The equivalent model of a supercapacitor helps to understand its performance under certain conditions, and also helps the developer to simulate their project in conditions that are not easy to achieve in practice. The simulation results are very important evidence that confirm the experimental results.

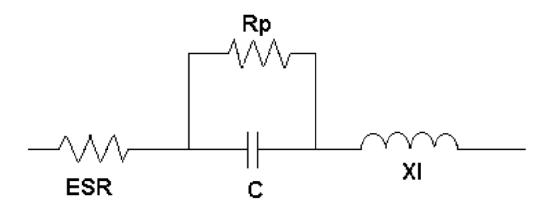

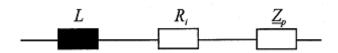

Typically the supercapacitor model is described as a RC circuit. An equivalent circuit in Figure 2.10 shows a first order model. It contains

- A capacitor *C*

- An inductor XI

- Rs Electrode dynamic representation of ESR (equivalent series resistance)

- A parallel resistance Rp representing as the energy leakage

Figure 2.10: The first order supercapacitor model (Illinois Capacitor INC., 2013)

However, this model cannot accurately describe supercapacitor behavior in the high frequency environment. Therefore a complex impedance model developed contains an inductor, a series resistance and the complex impedance, as shown in Figure 2.11.

Figure 2.11: Advance equivalent circuit of a supercapacitor (Schiffer, Linzen, & Sauer, 2006)

The equation 2.10 gives the mathematical expression for complex impedance  $Z_p$ .

$$\underline{Z}_{p}(j\omega) = \frac{\tau \cdot \coth(\sqrt{j\omega\tau})}{C \cdot \sqrt{j\omega\tau}}$$

(2.10)

(Buller, Karden, Kok, & De Doncker, 2002)

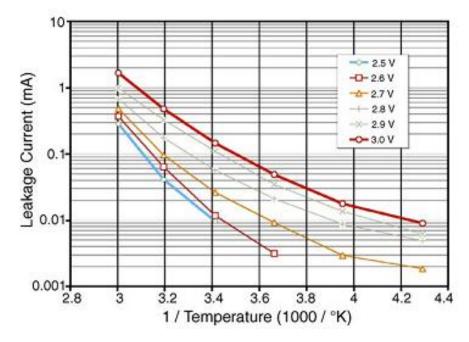

The leakage current is defined as a gradual loss of stored energy, which is also effected by the temperature variation. A logarithm of the leakage current is plotted in Figure 2.12 versus the reciprocal of the temperature in °K. (The measurements do not exhibit a straight line, which are only able to be used for leakage current estimation.)

Figure 2.12: Temperatures affect to the behavior of leakage current (Kötz et al., 2006)

# 2.16 Surge withstand capability

The supercapacitor surge withstand capability was evaluated by Nihal Kularatna and his team. The supercapacitors with different commercial brands have been used for the experiment, which included Cap-xx, Nesscap and Maxwell Boostcap; the electrical characteristics summarized in Table 2.1.

Table 2.2 A summary of test results applicable to the three supercapacitor families (Kularatna et al., 2011)

| Device data               | LSS                       | Number of surges to destroy the device |                                                                             |                                                                                                           |                                                                                                   |

|---------------------------|---------------------------|----------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|                           | output<br>peak<br>voltage | No pre-<br>charge                      | Pre-charge<br>voltage<br>=250mV                                             | Pre-charge<br>voltage =500mV                                                                              | Pre-charge voltage<br>=1.8V                                                                       |

| Cap-xx<br>0.18F, 2.3V     | 6.6kV                     | 220 to<br>over 250                     | Over 220                                                                    | Over 180                                                                                                  | Over 160                                                                                          |

| Maxwell 6.<br>230F, 2.5V  | 6.6kV                     | No pre-<br>charge                      | Pre-charge<br>voltage<br>=200mV                                             | Pre-charge<br>voltage =1.0V                                                                               | Pre-charge voltage<br>=2.5V                                                                       |

|                           |                           | Did not<br>fail after<br>1000          | Did not fail<br>after 600;<br>Charge<br>accumulation<br>was not<br>observed | Did not fail after<br>600; Over the<br>period of 700<br>repeated surges<br>0.1V discharge<br>was observed | Did not fail after<br>600; Over the period<br>of 700surges a<br>discharge of 0.2V<br>was observed |

| NessCap 6.6.<br>90F, 2.7V | 6.6kV                     | No pre-<br>charge                      | Pre-charge<br>voltage<br>=500mV                                             | Pre-charge<br>voltage =1.0V                                                                               | Pre-charge voltage<br>=2.0V                                                                       |

|                           |                           | Did not<br>fail after<br>600           | Did not fail<br>after 600; No<br>charge<br>accumulation<br>observed         | Did not fail after<br>600; Slight<br>discharge of<br>0.15V observed<br>during 700 surges                  | Did not fail after<br>600; Discharge of<br>approx 350mV was<br>observed over 700<br>surges.       |

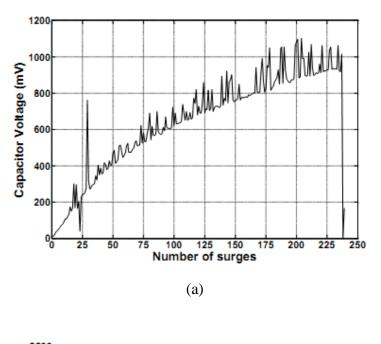

Those capacitors have been subjected to three different experiments:

- Uncharged supercapacitor with repeated surges applied.

- Repeated surges applied when the supercapacitors initially hold voltages.

- Repeated surges applied when the supercapacitors operated in voltage cycling.

Figure 2.13 (a) indicates the test sample of 0.18F supercapacitor from Cap-xx could easily withstand over 200 hits of 6.6kV surges before a failure. The surges

has absorbed and resulted in an increase of terminal voltages. In the pre-charging test (in Figure 2.13 b), the supercapacitor initially holding at high voltages (over 1.8V for 1.8F), which keeps discharge when surges applied. While low pre-charging voltages did not show the same effect.

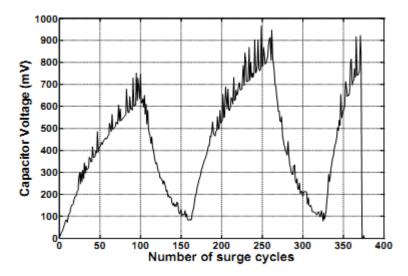

Figure 2.13: Waveforms show voltage across Cap-xx (0.18F, 2.3V) after repeated 6.6kV surges (a) uncharged supercapacitor, (b) with initial charge varying from 200mV to 1.8V (Kularatna et al., 2011)

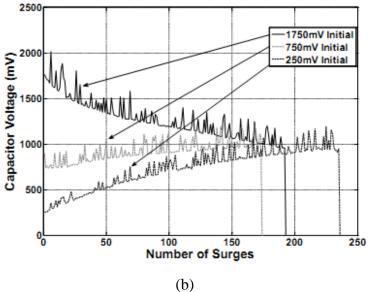

Repeated surges were applied to the supercapacitor of Cap-xx 0.18 F during the

voltage cycling. The Figure 2.14 demonstrates a failure after over 350 repeated surges were applied.

Figure 2.14: Surges are applied to charge the Cap-xx branded SC, after 100 surge applications SC discharges across a 200  $\Omega$  resistor. This is repeated until failure (Kularatna et al., 2011)

In summary, the supercapacitors present a robust surge withstand capability. This property can be used for developing the surge suppression system.

## 2.2 Charge circuit

This research is continual development based on original SRUPS. The major issue of previous design is the usage of a complicated charger. For this weakness, a flyback type charger proposed, which has advantages of minimum components contain and high common mode transient rejection. Therefore, next section will discuss fundamentals of flyback converter topology and transformer design.

#### 2.21 Flyback converter

Low cost and simplify are the major advantages of the flyback topology. The primary specifications for an off-line flyback power supply design are highlighted on the following (Kularatna, 2008):

• Nominal AC input voltage

- Minimum and maximum AC input voltage

- Output voltage

- Maximum output overshoot, full load to no load

- Target efficiency at full load

- Holdup time at nominal AC input voltage and full load at output

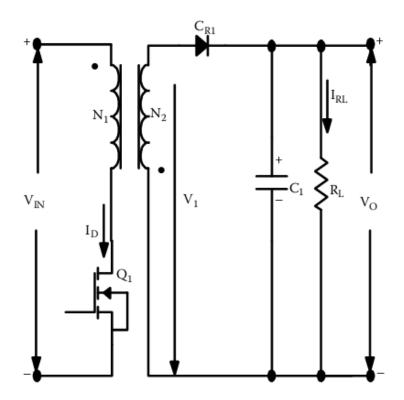

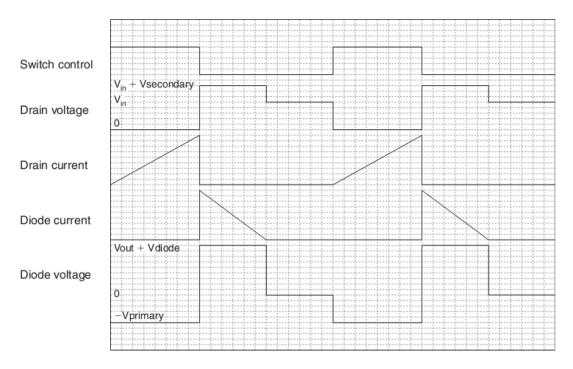

Principally, a switch (MOSFET or IGBT is shown as Q1 in Figure 2.15) is used to control the electrical energy storage via the primary winding, where the energy is stored while the switch is on, and the electrical energy is released to the secondary when the switch is off. A diode is on the secondary side that allows the current flow only when the switch is off.

Waveforms show in Figure 2.16, the primary windings get charged as presenting an increase of drain current, during the switch is on. The diode current indicates the energy transfer though the weak coupling to the secondary side, it happen during the switch is off. Switching circuits have parasitic inductance, as well as the transformer and diode have parasitic capacitance. Those will affect the charging circuit performance.

Figure 2.15 A flyback circuit (Kularatna, 2008)

Figure 2.16: Operational waveforms for the flyback circuit in discontinuous mode (Brown, 2007)

## 2.22 Transformer design

The flyback transformers operate in the flyback mode. Principally, a switch (MOSFET or IGBT) is used to control the electrical energy storage via the primary winding, where the energy is stored while the switch is on, and the electrical energy is released to the secondary when the switch is off. A diode is on the secondary side that allows the current flow only when the switch is off.

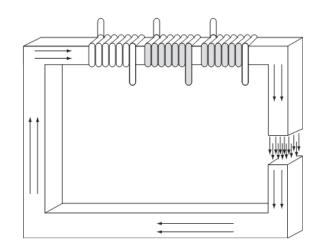

To improve the potential of energy storage, the transformer usually employs a ferrite core with an air gap as depicted in Figure 2.17. The energy highly concentrated in the air gap between the core face, because reluctance in the air gap is much higher than magnetic core. The major proportion of magnetic flux is cycling inside the ferrite core. However in practical applications, small amount flux will flow outside the magnetic circuit resulting in flux leakage. The occurrence of high magnetic flux concentrates in the air gap, which is used to improve the inductor saturation.

Figure 2.17: A ferrite core with three windings (Brown, 2007)

2.23 Continuous and discontinuous mode

A flyback circuit is able to operate in either continuous or discontinuous mode. In the continuous mode (in Figure 2.18 b), inductor current of all windings never reach zero. In the discontinuous mode, the energy releases from the transformer primary (energy store in the primary inductor) decreases and finally goes to zero, thus the zero current occurs in the all the windings during a part of cycle. The discontinuous current waveforms are depicted in Figure 2.18 (a).

(a) The current waveform in the discontinuous mode

(b) The current waveform in the continuous mode

Figure 2.18: The waveforms of winding current in (a) discontinuous mode and (b) continuous mode (Dixon, 2000)

Both of continuous and discontinuous modes have advantage and disadvantage. The primary advantage of continuous mode is that the current ripple in the conductor is relatively smaller. It requires a simpler smoothing circuit at the transformer secondary side. The peak current compare to discontinuous mode is almost one – half at the same power level. However, a complicated control loop is necessary to keep the current fluctuation in a small window.

The discontinuous mode circuit is used to operate in large peak current. The advantage is that lower thermal stresses drop on the transformer switch, because the current begins from zero and only portion of the input voltage is applied to the switch. The inductor current drop back to the origin at every end of cycle, therefore reserve current across the diode can be negligible, which avoid the diode reserve breakdown. However a requirement of higher inductance of all of transformer windings, because it is efficiently saturated under the high peak current force.

When the flyback transformers are either operated in the continuous or discontinuous mode, the current in each winding is always highly discontinuous, regardless of inductor current mode. However, the continuous mode exhibits lower core loss because of smaller current ripple.

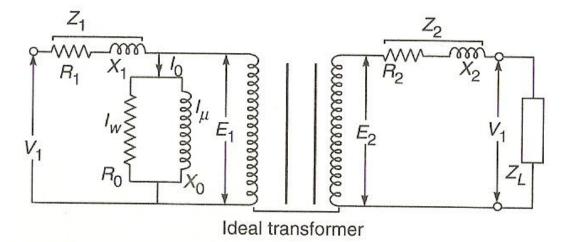

2.4 Transformer equivalent circuit

The equivalent of ideal transformer shows in Figure 2.20, which helps to understand the energy transfer behavior. The resistance and leakage reactance of the transformer are imagined to be external to the winding. The no-load current  $I_o$  divides into two parallel branches. The pure inductances  $X_o$  carry the magnetizing component  $I_u$ , and non-inductive  $R_o$  carry the active component  $I_w$ .

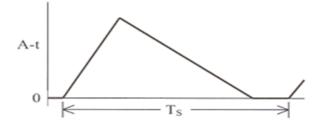

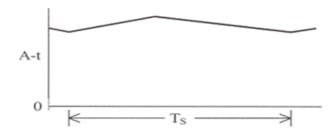

The magnetizing component  $I_u$  is 90° behind the  $V_1$  because of inductance, while the active component  $I_w$  is in phase with  $V_1$ . Hence the no-load primary input current is the vector sum of  $I_w$  and Iu, which lags  $V_1$  by an angle  $\theta$ . The vector diagram of primary input current shows in Figure 2.19.

As seen from Figure 2.19, the primary current has two components.

• The active component  $I_w$  is in phase with  $V_1$ , which is taking the iron-loss plus the copper-loss of primary winding.

$$I_w = I_0 \cos \theta_0$$

(2.11)

(Bharat Heavy Electrical Limited, 2003)

• The magnetizing component is in quadrature with  $V_1$ , its expression can be presented as

$$I_{\mu} = I_0 \sin \theta_0 \tag{2.12}$$

(Bharat Heavy Electrical Limited, 2003)

• The Io is the vector sum of  $I_w$  and  $I_u$ , hence

$$I_0 = \sqrt{I_\mu^2 + I_w^2}$$

(2.13)

(Bharat Heavy Electrical Limited, 2003)

• *R*<sub>1</sub> and *X*<sub>1</sub> represent the transformer input resistance of primary winding. Hence the primary impedance is given by

$$Z_1 = \sqrt{(R_1^2 + X_1^2)}$$

(2.14)

(Bharat Heavy Electrical Limited, 2003)

• R<sub>2</sub> and X<sub>2</sub> represent the leakage reactance of secondary winding, the secondary impedance is given by

$$Z_2 = \sqrt{(R_2^2 + X_2^2)}$$

(2.15)

(Bharat Heavy Electrical Limited, 2003)

And

$$\begin{split} V_1 &= E_1 + I_1 \left( R_1 + j X_1 \right) = E_1 + I_1 Z_1 \\ E_2 &= V_2 + I_2 \left( R_2 + j X_2 \right) = V_2 + I_2 Z_2 \end{split}$$

(2.16)

(Bharat Heavy Electrical Limited, 2003)

Figure 2.20: A model for an ideal transformer (Bharat Heavy Electrical Limited, 2003)

### 2.25 Energy losses in the transformer winding

### 2.251 Hysteresis losses

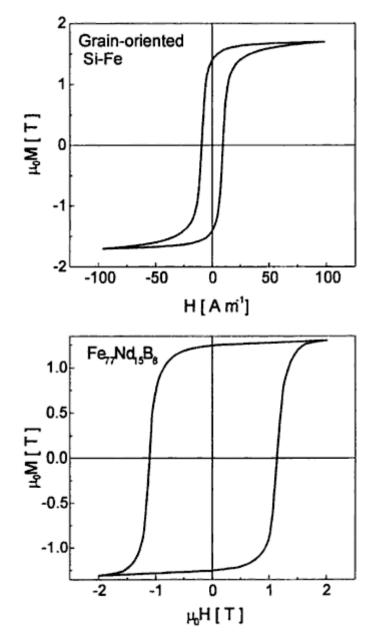

Hysteresis loop presents energy lost in the core. The large area of hysteresis loop is associated the high energy lost, Figure 2.21 shows the hysteresis loop curves due different ferrite materials. This phenomena occurs because of the flux density B is always lag behind the field intensity H. The loss occurs on every half cycle when the magnetic field reserves the direction, and energy is expended. To reduce the loss, a ferrite core with low hysteresis is required. In general, hysteresis losses will increase with frequency. To accurately calculate the hysteresis losses regarding the high frequency consideration, please refer to references of soft ferrites written by Snelling and 2.21, which the equations are available.

Figure 2.21: Hysteresis loops with different factors (Bertotti, 1998)

## 2.252 Eddy current losses

Figure 2.22 the symmetrical flied surround an around conductor that is carrying direct current (DC) or low frequency current. The energy losses are due to the DC resistance, which associate to the dimension of cross sectional area of conductors.

Figure 2.22: Uniform current flows in a conductor at low frequency (Dixon Jr, 1988)

Figure 2.23 depicts what happen when high frequency current flow in the conductors. The dash lines represent the uniform low frequency current distribution, and the circular lines represent the high frequency current distribution. The flow direction of current changes rapidly due to the high frequency, as well as the flux within the conductor is also changed rapidly. The result is that as frequency rises, where the current tends to concentrate towards the conductor skin, with a decrease of current density at the conductor center. Figure 2.24 describes that the current density at conductor center will tail off exponentially and toward zero if the frequency is rising continuously. Hence only potion of conductor carries the total current. In other words the conduct area is much smaller than the same conductor carrying low frequency current.

Figure 2.22: Eddy current at high frequency (Dixon Jr, 1988)

Figure 2.23: Current distributions at high frequency (Dixon Jr, 1988)

Penetration depth is defined as the distance from the surface to where the current density is 1/e times the surface current density ( is the natural log base )

$$D_{PEN} = [\rho/(\pi\mu f)]^{1/2}$$

m

(2.17)

(Dixon Jr, 1988)

$$D_{PEN} = 7.5(f)^{1/2}$$

cm

(2.18)

(Dixon Jr, 1988)

The equations of 2.17 and 2.18 are accurate for a flat conductor surface. For the curveted surface the actual penetration depth is smaller than the calculation.

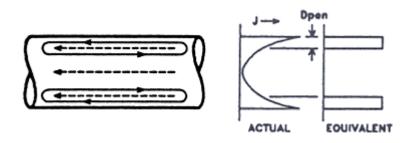

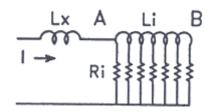

A equivalent circuit mode in Figure 2.24 demonstrates current behavior at high frequency. When the current (I) flow into  $L_X$  that represents inductance of the wire at high frequency. The energy store in the external magnetic field  $L_X$  will be  $0.5 L_X I$ . Point A represents the outer surface of the conductor, and B is internal. The resistance from the surface to the center divides into many concentric cylinders of equal cross section area, which are represented as Ri. The internal inductance Li store energy through the cylindrical sections. The energy store in each section depends on the cumulative current flowing through those elements from the left to the right. The external inductance  $L_X$  (represents leakage inductance of the winding) and the source compliance voltage limits the maximum charge radio of the wire, regardless of how fast the switch turns on.

Figure 2.24: Equivalent circuit of a conductor (Dixon Jr, 1988)

# 2.26 Proximity effect

Proximity effect defines that two close wire carrying equal current in the opposite direction, the magnetic field generated by the wires will cancel each other. This cancellation will results in the concentrated field volume decreases, thus the inductance is reduced.

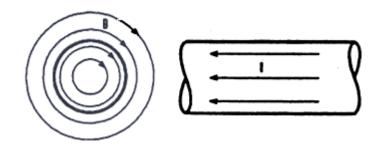

2.27 Multiple layers

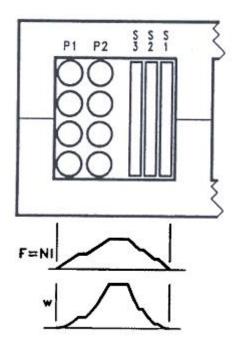

Many transformer applications consist of multiple layers in order to reduce the size of the transformer. Figure 2.25 shows a transformer with multiple layers carrying a low frequency current and the energy density diagrams. At low frequency current (not shown) is uniformly distributed through all windings, because they are much thinner than the penetration depth. The energy diagram shows energy density concentrate and peak at center, and present minor leakages. However at the high frequency, the eddy current losses increase exponentially due to multiple layers.

Figure 2.25: Multiple layer windings (Dixon Jr, 1988)

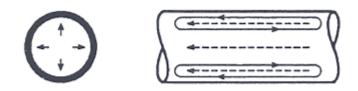

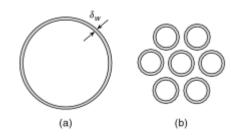

2.28 Litz wires

The first transformer made for this research presented high energy losses. The reason for those losses was due to winging made of solid wires. The resistance of solid wire at low frequency is associated on their across sectional area. Larger cross section area results in the lower resistance. However a charging circuit designed for this research operated at high frequency in the range of 50 kHz. In the high frequency environment, the current is concentrated close to the conductor surface, which results reduction of cross sectional area, while the AC resistance of conductor is increased. The litz wire is used as an alternative conductor to minimize the energy losses that exhibit in the solid wire, as well as to eliminate proximate effect. It consists of many isolated wires, which are stranded and twisted to form a rope. The standard twist configuration is 18 - 36 twists per meter, and typical diameters of the strands are 0.05, .071, 0.1, 0.15, 0.2 and 0.8 mm (Sullivan, 1997). It usually protected by nylon textile or yarn, in order to add the extra strength. The litz wire increases the surface area without increasing the net size of conductor. Figure 2.26 shows both wires have almost same net diameter, but litz wire provides larger surface area. The overall eddy current loss at high frequency represent as

$$P_{loss} = F_r I_{ac}^2 R_{dc}$$

(2.19)

(Sullivan, 1997)

Where :

- $F_r$  is a factor relating to DC resistance to AC resistance which accounts for all winding losses.

- $I_{ac}$  is root mean square (rms) value of sinusoidal current.

- $R_{dc}$  is DC resistance of winding.

The approximation effect can be expressed as

$$F_r = 1 + \frac{\pi^2 \omega^2 \mu_0^2 N^2 n^2 d_c^6 k}{768 \rho_c^2 b_c^2}$$

(2.20) (Sullivan, 1997) Where :

- $\omega$  is the radian frequency of AC current.

- $\rho_c$  is the resistivity of copper conductor.

- *N* is the number of turns.

- *n* is the number of strands.

- $B_c$  is the breadth of the window area of the ferrite core.

- *K* is a factor of net field distribution.

The resistance of litz wire winding is independent of the number of layers, assume the DC resistance of litz wire is similar to the solid wire, it can be expressed as

$$\frac{4\rho_w\iota_w}{\pi d^2} = \frac{4\rho_w\iota_{w\iota}}{n\pi d_{\iota}^2}$$

(2.21)

(Sullivan, 1997)

Obtain the number of strands, equation is rearrange as:

$$n = \frac{\iota_{w\iota}}{\iota_w} (\frac{d}{d\iota})^2$$

(2.22) (Sullivan, 1997)

Figure 2.26: The litz wire has larger surface area than a round solid wire, (a) solid wire, (b) litz wire (Sullivan, 1997)

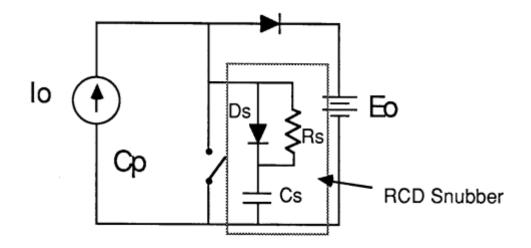

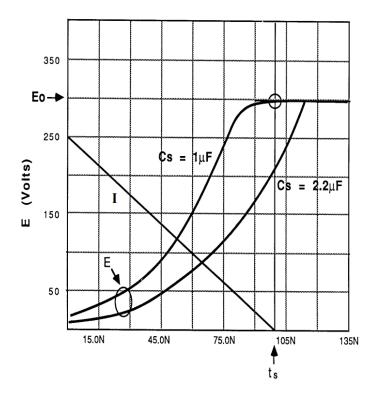

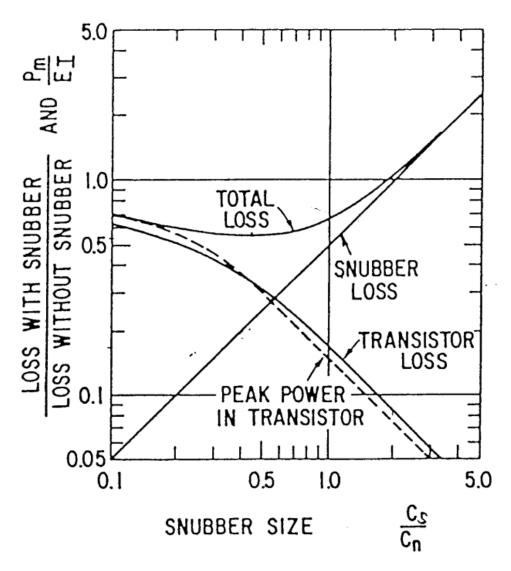

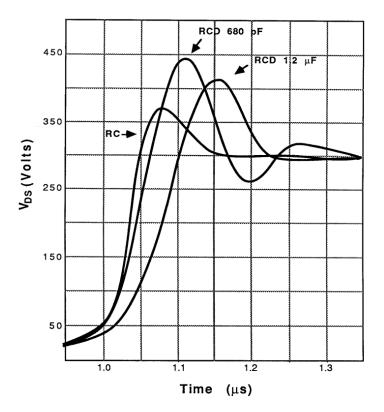

2.29 Snubbers

Snubber is a protection circuit where the circuit configuration is very simple. Two typical arrangements are the resistor–capacitor (RC) damping network and the resistor–capacitor–diode (RCD) snubber. They are usually placed across the switches to limit the clamping voltage on the switches, as well as to improve the switching performance. The main purposes of the snubber are:

- Limit or eliminate voltage or current spike across switches

- Limit the clamping voltage on the switches

- Reduce total loss due to switching

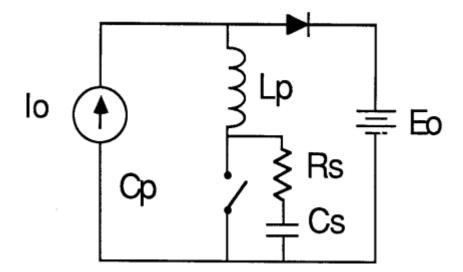

## 2.291 Resistor-capacitor snubber design

The resistor-capacitor (RC) snubber consists of a resistance ( $R_s$ ) and capacitor ( $C_s$ ), which is connected across the switch in parallel, the Figure 2.27 demonstrates a typical RC snubber circuit. For the RC snubber must obey  $C_s > C_p$ . Cs usually chooses as twice the sum of the output capacitance of the switch and the estimated mounting capacitance.  $R_s$  is selected so that  $R_s = E_o/I_o$ . Hence the voltage across the RC network due to the initial current flowing in  $R_s$  is no greater than the clamped voltage. The power dissipation in Rs can be estimated from peak energy stored in  $C_s$ :

$$U_p = \frac{C_s E_0^2}{2}$$

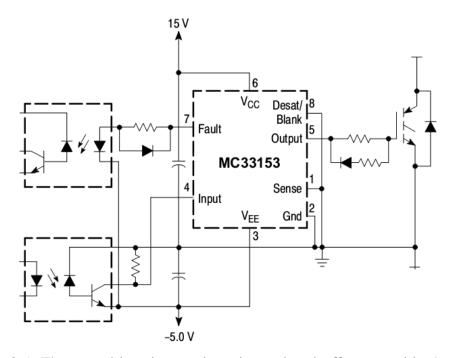

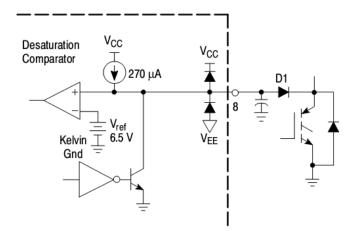

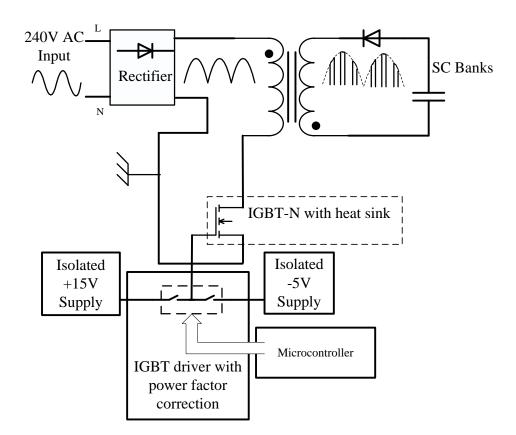

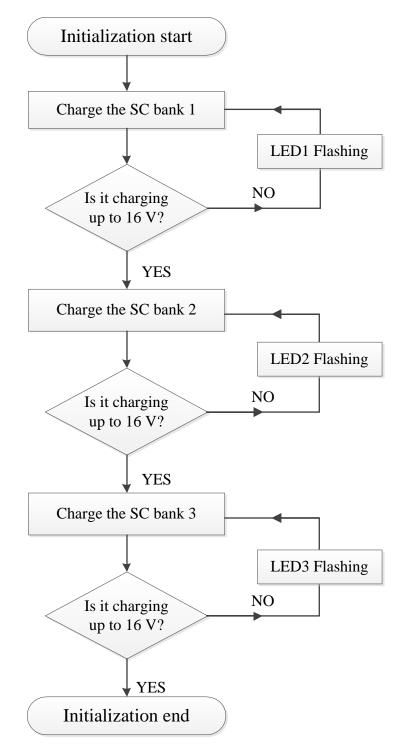

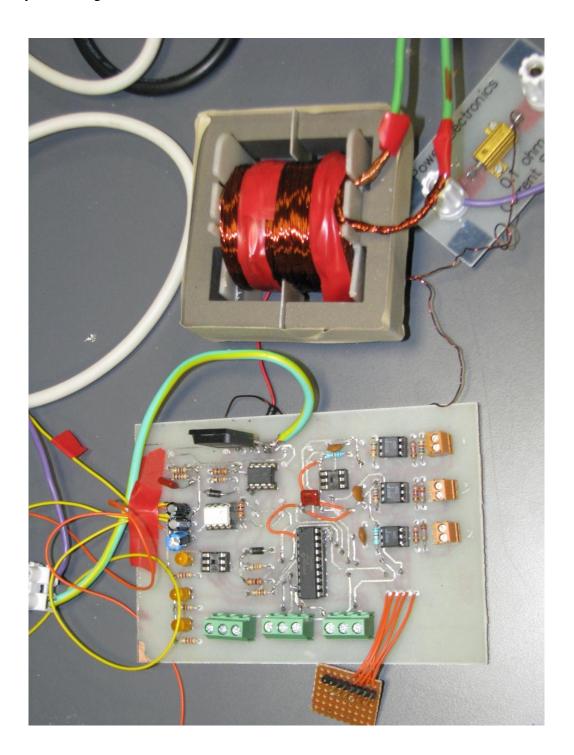

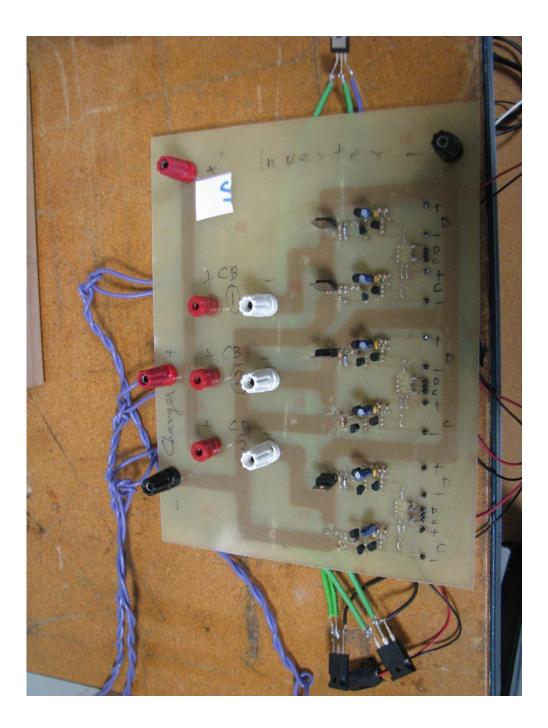

(2.23) (Severns, 2006)