### http://waikato.researchgateway.ac.nz/

### **Research Commons at the University of Waikato**

### **Copyright Statement:**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

The thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of the thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from the thesis.

# Selection of Components in Compositional Verification of Safety Properties

Jinjian Shi

This thesis is submitted in partial fulfillment of the requirements for the Degree of Master of Science at the University of Waikato.

July 2009 © 2009 Jinjian Shi

## **Abstract**

This report presents a two-step components selection method to compose the components for compositional verification. This method employs different methods for the selection of components to be composed during compositional verification. Also, this report presents some automata transformation strategies to improve the efficiency of composing and projection. This enhanced compositional verification method is applied to a set of large and complex realistic industrial examples to evaluate and compare the performance of different methods for components selection. The example *profisafe\_i6* [MM03] [MM02] [PN02], which was never verified for the language inclusion check before, is verified first by this enhanced compositional verification method.

## **Contents**

| Chapter 1 Introduction   |                        |  |  |  |

|--------------------------|------------------------|--|--|--|

| Chapter 2 Preliminaries5 |                        |  |  |  |

| 2.1 A                    | utomata Theory5        |  |  |  |

| 2.1.1                    | Automaton5             |  |  |  |

| 2.1.2                    | Event6                 |  |  |  |

| 2.1.3                    | Transition             |  |  |  |

| 2.1.4                    | Automata Type8         |  |  |  |

| 2.2 Sy                   | vnchronous Product     |  |  |  |

| 2.3 Sa                   | fety Property10        |  |  |  |

| 2.3.1                    | Controllability        |  |  |  |

| 2.3.2                    | Language Inclusion     |  |  |  |

| 2.3.3                    | Counterexample         |  |  |  |

| 2.4 Pr                   | ojection               |  |  |  |

| 2.5 M                    | odel Checker           |  |  |  |

| 2.5.1                    | Native Model Checker   |  |  |  |

| 2.5.2                    | BDD Model Checker      |  |  |  |

| 2.5.3                    | Modular Model Checker  |  |  |  |

| 2.6 Ex                   | xamples for Evaluation |  |  |  |

| 2.7 Im                   | pplementation          |  |  |  |

| Chapter | 3 Enhanced Compositional Verification                         |

|---------|---------------------------------------------------------------|

| 3.1     | Introduction                                                  |

| 3.2     | Algorithm2                                                    |

| 3.3     | Counterexample Extension for Projection24                     |

| Chapter | 4 Automata Transformation                                     |

| 4.1 A   | utomata Conversion                                            |

| 4.1.1   | Introduction                                                  |

| 4.1.2   | Automata Conversion for Controllability Check                 |

| 4.1.    | 2.1 Specification Automata Conversion                         |

| 4.1.    | 2.2 Plant Automata Conversion                                 |

| 4.1.    | 2.3 One-state specification creation                          |

| 4.1.    | 2.4 Evaluation                                                |

| 4.1.3   | Automata Conversion for Language Inclusion Check              |

| 4.1.    | 3.1 Property Automata Conversion                              |

| 4.1.    | 3.2 Non-property Automata Conversion                          |

| 4.1.    | 3.3 One-state property creation                               |

| 4.1.    | 3.4 Evaluation                                                |

| 4.1.4   | Counterexample Correction for Automata Conversion49           |

| 4.2 A   | utomata Simplification                                        |

| 4.2.1   | Introduction                                                  |

| 4.2.2   | Selfloop Check                                                |

| 4.2.3   | Same Transition Check                                         |

| 4.2.4   | Almost Same Transition Check                                  |

| 4.2.5   | Counterexample Correction for Almost Same Transition Check 55 |

|    | 4.2.6    | Evaluation                                                           | 58 |

|----|----------|----------------------------------------------------------------------|----|

| C  | hapter 5 | Candidates Construction and Selection                                | 66 |

| 5. | 1 Can    | didates Construction                                                 | 67 |

|    | 5.1.1    | Introduction                                                         | 67 |

|    | 5.1.2    | MustL candidates construction algorithm                              | 67 |

| 5. | 2 Heu    | ristic MaxL                                                          | 70 |

|    | 5.2.1    | Introduction                                                         | 70 |

|    | 5.2.2    | Algorithm for calculating proportion of local events                 | 71 |

| 5. | 3 Heu    | ristic MinS                                                          | 72 |

|    | 5.3.1    | Introduction                                                         | 72 |

|    | 5.3.2    | Algorithm for predicting the number of states of the synchronous     |    |

|    | product  |                                                                      | 73 |

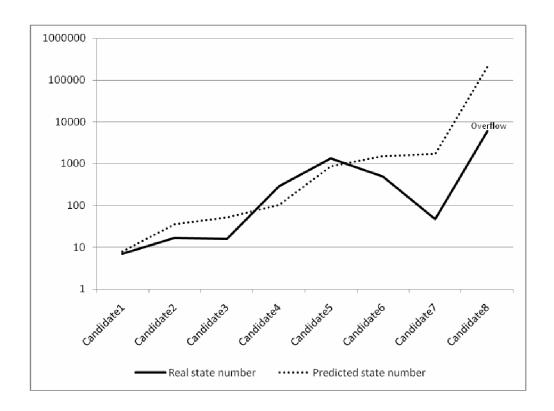

|    | 5.3.3    | Number of states prediction evaluation                               | 75 |

| 5. | 4 Heu    | ristic MinT                                                          | 78 |

|    | 5.4.1    | Introduction                                                         | 78 |

|    | 5.4.2    | Algorithm for predicting the number of transitions of the synchronou | s  |

|    | product  |                                                                      | 79 |

|    | 5.4.3    | Number of transitions prediction evaluation                          | 80 |

| 5. | 5 Heu    | ristic MinCut                                                        | 84 |

|    | 5.5.1    | Introduction                                                         | 84 |

|    | 5.5.2    | Algorithm for calculating the cut number                             | 86 |

| 5. | 6 An 1   | Enhancement for Candidates Construction                              | 89 |

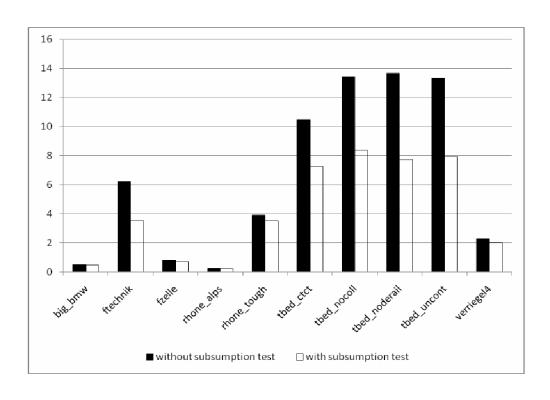

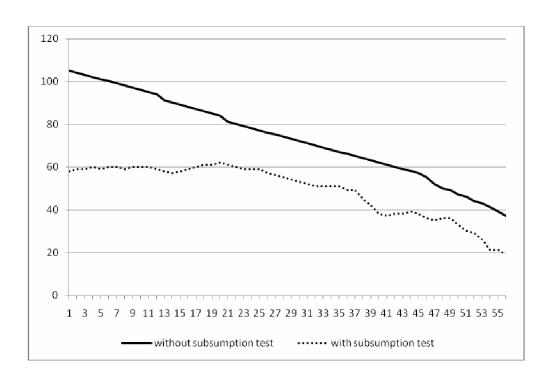

|    | 5.6.1    | Subsumption                                                          | 89 |

|    | 5.6.2    | Subsumption evaluation                                               | 91 |

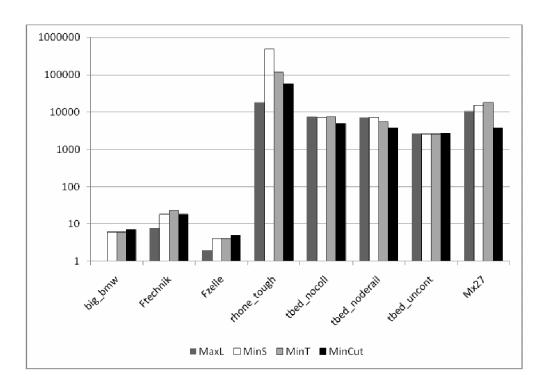

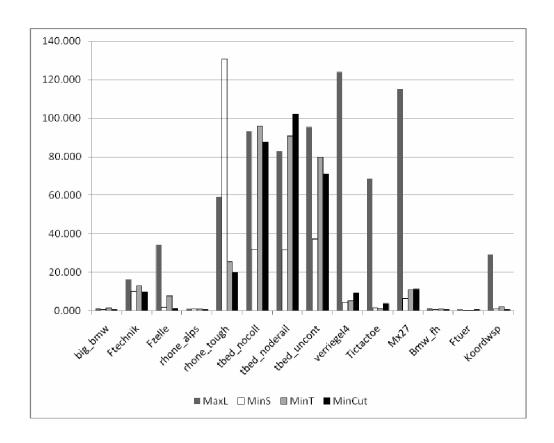

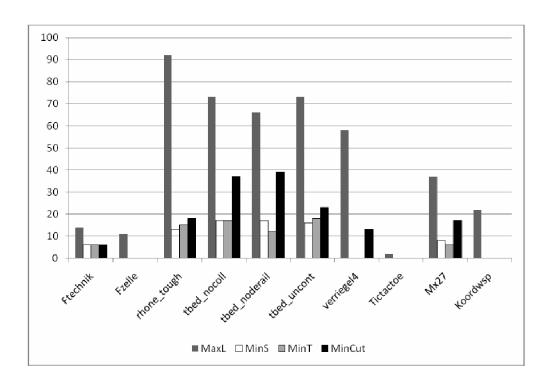

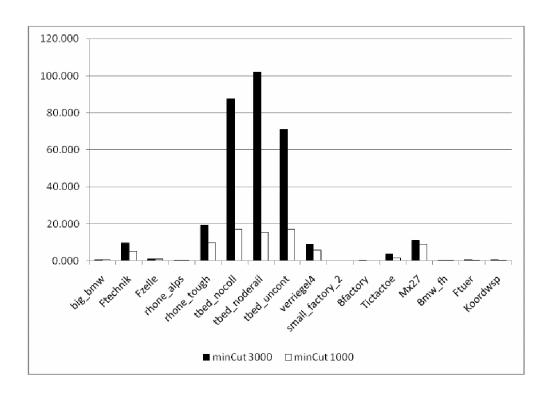

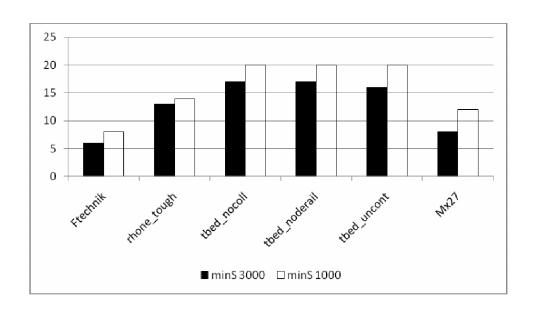

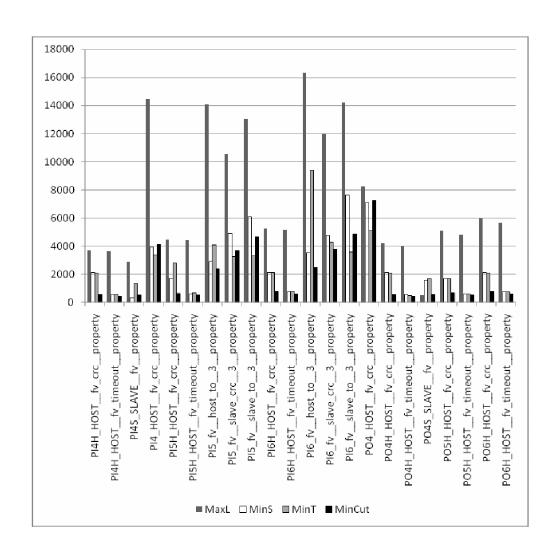

| 5.7                                         | Eva | aluation                         | 98  |

|---------------------------------------------|-----|----------------------------------|-----|

| 5.7                                         | .1  | Introduction                     | 98  |

| 5.7                                         | .2  | Controllability Check Results    | 100 |

| 5.7                                         | .3  | Language Inclusion Check Results | 105 |

| Chapter 6 Conclusion                        |     |                                  | 114 |

| References                                  |     |                                  | 116 |

| Appendix Compositional Verification Results |     |                                  | 120 |

## **Chapter 1**

## Introduction

Safety is always the first issue which should be considered when designing a system. In a software system, the safety and reliability of software are the most important quality characteristics [MJD99]. Especially in industry, a precise safety-concerned design may save a lot of time, money, and even life. In order to design the system right and make the system reliable and safe to be used, there is a need to verify the model of the system. Verification is a measure to check the safety of the model and ensure the model is built correctly. According to Balci, "Verification deals with building the model right" [OB97], this is the objective of the term "verification". Therefore, verification of safety properties is crucial and necessary for system design in order to build a right system. However, with increasing requirements and competition, systems become more powerful, more functional, and more effective. Meanwhile, with the development and upgrade of systems, their numbers of components are increasing and their complexities are mounting up, and the trend will continue in the future. This makes verification become a challenge because of the larger and more complex systems.

Usually, a model checker for verification constructs a synchronous product of the model of a system in order to verify it. But it may encounter a problem of state-space explosion for models with a large number of components when constructing a synchronous product. This may cause the model checker to run out of time or out of memory.

1

The Native model checker [BBFLPP98], [JS06] and BDD model checker [BBFLPP98], [REB86] are two model checkers which construct the synchronous product by composing all components of the model. Both of them encounter the problem of state-space explosion easily, even though the BDD model checker represents the state space symbolically in order to save space.

The Modular model checker [SW07], [BMM04] cuts down the state space consuming by analyzing the synchronous product of subsets of the components of the model instead of the synchronous product of the entire model. So are compositional verification and incremental verification [BMM04], [AFF02]. These three methods obtain improvements for large verification, but the problem of state-space explosion problem still exists.

The Projecting model checker [SW07], [WM08] simplifies the size of the model by projecting some events out and then reducing the state space of synchronous product. This method enhances extremely the performance of verification for large models, but it still has some potential to be improved.

This report presents an enhanced compositional verification method for language projection to reduce the state-space explosion problem. It uses a two-step method to select a set of automata, which is called a candidate, of the system to be composed. The first step is constructing a series of candidates based on the method mustL [FM06]. The second step is selecting the best candidate from the series of candidates according to a certain heuristic which could be maxL, minS, minT [FM06], or minCut. MinCut is first introduced in this report. After the candidate is chosen, projection is activated to compose all of the automata in the candidate into one automaton and project some events out to reduce the size and

complexity of this new automaton.

In order to improve the compositional verification of safety properties, and project more events, a strategy named Automata Conversion [SW07], [WM08] is applied. As for the controllability check, this strategy converts the controllability problem into the language inclusion problem. Instead of checking whether uncontrollable events are enabled at a bad time, it only checks if a certain event can ever happen. This strategy converts all specification automata into plant automata by adding some selfloops and creates a new singleton-state specification automaton which declares what uncontrollable events cannot happen. Ideally, after composing and projection, the final model will have one state if the system is not controllable or zero states if the system is controllable. As for the language inclusion check, this strategy is still working by converting the property automaton into plant and creating a new singleton-state property automaton which tells what bad events can never happen, too.

Furthermore, more improvements are made for enhancing the compositional method. In this project, subsumption test is adopted to remove some unnecessary candidates from the candidates list and reduce the size of it; Selfloop check, Same Transition check, and Almost Same Transition Check are also introduced in order to minimize the size of automata further.

Since projection is introduced in this project, the counterexample is not original any more. Some of the events are projected. Therefore, a backward solution [SW07] is taken to extend the counterexample trace. Also, Almost Same Transition Check could change the trace, but will not change the length of the trace. Hence, the counterexample after Almost Same Transition Check needs to be corrected, too.

This enhanced compositional verification method is applied to a set of large and complex realistic industrial examples to evaluate and compare the performance of four different methods for components selection, and implemented as a toolkit of WATERS [WS]. The example *profisafe\_i6* [MM03] [MM02] [PN02], which was never verified for the language inclusion check before, is verified first by this enhanced compositional verification measure.

Chapter 2 presents some of the required knowledge for understanding of this thesis. Chapter 3 describes compositional verification and its algorithm. Chapter 4 presents the strategies of Automata Conversion and Automata Simplification. Chapter 5 discusses the method to construct the candidate list, and the heuristics employed for candidate selection in compositional verification and compares the performance of them according to the experimental data. Chapter 6 presents the conclusion of this project.

## **Chapter 2**

## **Preliminaries**

### 2.1 Automata Theory

Automata theory is widely used in computer science for analyzing and verifying the finite state model of a system. It is the study of a theoretical model of software systems or computer hardware [MS05].

#### 2.1.1 Automaton

An automaton is a mathematical model for a finite-state machine. Usually, the aim of it is to study the capabilities and limitations of computing processes. A finite-state automaton (finite-state machine) is a machine that, given an input of symbols, jumps from one state to another according to the action of transitions. Formally, a finite-state automaton is described as a tuple [BBFLPP98]

$$A = (Q, \Sigma, T, q_0, Q_m)$$

with

finite set of states  $Q = \{q_1, q_2, q_3, ...\}$

finite set of events  $\Sigma = \{a, b, c, ...\}$

transition relation  $T \subseteq Q \times E \times Q$

initial state

$$q_0 \in \mathcal{Q}$$

set of marked states  $\mathcal{Q}_{\mathrm{m}} \subseteq \mathcal{Q}$

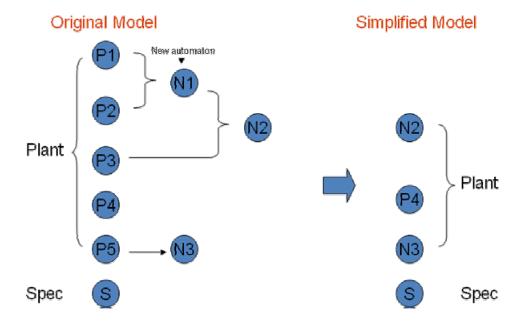

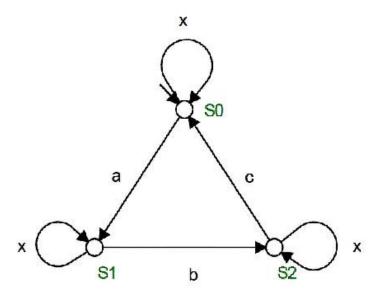

For example: the following is an example automaton.

Figure 2.1: An example automaton

According to Figure 2.1 and the definition of automaton, it displays that the finite state set Q is  $\{s_0, s_1\}$ ; the finite event set  $\Sigma$  is  $\{a, b\}$ ; there are two transitions which are  $s_0 \rightarrow s_1$  labeled with event a and  $s_1 \rightarrow s_0$  labeled with event b; the initial state is  $s_0$  which is an element of Q; and the marked state set is  $\{s_1\}$  which is a subset of Q. Putting these information together, it makes up the complete automaton.

#### **2.1.2** Event

In an automaton, events are used to connect states. An event may be moving up or down of an elevator, arrival or leaving of a train, termination of a computer program, start or finish of a task in a manufacturing factory, and so on.

An event is an occurrence or an action affecting the state change of a finite-state

automaton [KG95]. For instance, in Figure 2.1, both "a" and "b" are events. State  $s_0$  can go to state  $s_1$  when event a happens in state  $s_0$ . And state  $s_1$  can go back to state  $s_0$  when event b happens in state  $s_1$ . There is one important thing for event is hidden selfloop. Events which are not described in an automaton can happen at any time and anywhere, but it will not affect the change of state. For example, event c is not mentioned in Figure 2.1 above,

Figure 2.2: An example of Hidden Selfloop

So c is not in set E but it can happen at any states anytime (both at state  $s_0$  and  $s_1$ ) as showed in Figure 2.2. Nevertheless, the happening of event c does not change the state. Then c is a hidden selfloop event and the transition labeled with c is a hidden selfloop transition. These selfloops are implicitly added to all states.

#### 2.1.3 Transition

A transition is a passage from one state to another in an automaton [BBFLPP98]. It contains a source state, an event and a target state. For example,  $s_0 \rightarrow s_1$  labeled with event a and  $s_1 \rightarrow s_0$  labeled with event b are two transitions.

#### 2.1.4 Automata Type

In this project, there are three types of automata which are plant automaton, specification automaton, and property automaton.

A plant automaton is an automaton representing a model of the system to be controlled. It describes all of the possible behaviors of the model [BBFLPP98].

A specification automaton is an automaton designed to control the plant. It restricts the behavior of the plant by dynamically disabling some of the controllable events to avoid some undesired uncontrollable events happen [BBFLPP98]. So, it describes the desired behaviors.

A property automaton is an automaton which states that something bad should never happen [BBFLPP98]. For example, an elevator will never stop at the middle of two floors.

### 2.2 Synchronous Product

Systems are modeled using more than one automaton in real life, and they interact with each other when they run in parallel. When automata run in parallel, they all run at the same time. Therefore, the events can happen only if they can be accepted by all automata. In order to verify a system, it is needed to find a way to represent the entire system running in parallel. The synchronous product [BBFLPP98] is such a way to represent the system and the interaction of its components.

The synchronous product describes the current state of the whole system with a state tuple  $q = (q_1, q_2, \dots q_n)$  [BBFLPP98].

For example, there are two automata:

Figure 2.3: Two example automata

At first, both of them are at initial state, so the system composed by these two automata can be represented as  $(s_0, s_0)$ . In Figure 2.3, there are three available events which are event a, b, and c. As for automaton  $A_1$ , according to the definitions of selfloop, event a and c are enabled in the initial state while event b is not enabled, because event b is mentioned in this automaton but only enabled in state  $s_1$ . And for automaton  $A_2$ , event a and b are enabled while event c is not enabled for the similar reason with event b in  $A_1$ . Hence, as for the entire system, only event a is enabled in the initial state by all automata. When event a happens, the system state goes to  $(s_1, s_1)$ . In this state, both event a and a are enabled by the system, but not event a because it is only enabled by all automata in the initial state. Therefore, when event a happens, the current system state becomes a0, a1 from a1, a2, a3, and when event a3 happens, the current system state becomes a3, a4, a5, a6, a7, a8, a8, a9, a

happens and return to  $(s_0, s_0)$  from  $(s_1, s_0)$  when event b happens. In the example above, the system representation  $(s_0, s_0)$ ,  $(s_1, s_1)$ ,  $(s_0, s_1)$ ,  $(s_1, s_0)$  are the synchronous product states. The complete synchronous product is displayed in Figure 2.4:

Figure 2.4: An example Synchronous Product

## 2.3 Safety Property

A safety property is a property indicating that something bad can never happen [BBFLPP98]. It aims to keep the system safe. In this project, there are two safety properties, which are controllability and language inclusion.

#### 2.3.1 Controllability

In general, there are two types of event which are controllable events and uncontrollable

events. A controllable event is an event which can be disabled and enabled. An uncontrollable event is an event which cannot be prevented from happening.

Let P (Plant) and S (Specification) be two automata. S is called controllable with respect to P if, for every state  $(q_p, q_s)$  reachable in the synchronous product of P and S, every uncontrollable event e which is enabled in  $q_p$  also is enabled in  $q_s$  [RW89].

As for controllability, plant automata and specification automata are considered only. The specifications send controllable events to the plants and tell the plants what to do, while the plants send back uncontrollable events to the specifications and tell the specifications what has happened to them. The idea of designing the specification is to limit the behaviors of the plant in order to make the plant behave as desired. However, is it possible that the specification automata can limit the behaviors of the plant automata? In order to know the possibility, it is needed to check the controllability of the system which includes both the plants and the specifications. If this system is controllable, then the specifications can limit the behaviors of the plants; that is to say that for any reachable states of the plants, if an uncontrollable event can happen, then the specifications should also allow this uncontrollable event to happen. Otherwise, if this system is not controllable, that is to say that an uncontrollable event is enabled in the plants but it is not enabled in the specifications, and then the specifications cannot limit the behaviors of the plants because an uncontrollable event cannot be prevented from happening.

For example, as for the system in Figure 2.3, assume that  $A_1$  is a plant automaton and  $A_2$  is a specification automaton. Then in state  $(s_0, s_1)$ ,  $A_1$  allows event a and event a to happen while a0 only allows one event out of these two events to happen which is event a0. Therefore, if event a1 is an uncontrollable event, then this

system is not controllable because specification  $A_2$  disables an uncontrollable event a while it cannot be disabled.

#### 2.3.2 Language Inclusion

This project only considers deterministic discrete event systems (DES). The behavior of a deterministic DES can be described by the set of sequences of events [RW89]:

$$\sigma_0 \sigma_1 \dots \sigma_n$$

and the initial state  $s_0$ . One of these kinds of sequences of events is called a trace or string of the system, and a collection of traces is called a language.

Language inclusion is used to check if the language of a model is included by the language of a given automaton [BMM04]. This given automaton is a property automaton. For example, if and only if every trace in the language of a set of automata A is also in the language of property automaton B, then A satisfies B.

As for language inclusion, plant automata and specification automata are treated as the same automata which are non-property automata. The algorithm to check if the non-property automata satisfy the property automaton is to construct the synchronous product of both of the non-property automata and the property automaton, and check that if whenever all non-property automata enable an event, the property automaton will enable this event too. If this event is always enabled, then this property automaton is satisfied.

#### 2.3.3 Counterexample

A counterexample is a sequence of events which a specific instance of the falsity of a model. The counterexample trace represents that a bad event can happen eventually. If a model is failed to pass the verification of safety properties, then the model checker will automatically compute such a counterexample.

[BBFLPP98]

## 2.4 Projection

There exist some events that are used exclusively by only one automaton or a set of automata, or can be removed away for other reasons in some large systems composed of several automata. As a result, the alphabet  $\Sigma$  is partitioned into the set Y of events to be removed away and the set  $\Omega$  of events to be retained. Typically, Y consists of the events used exclusively by the automata considered.

Natural projection

$$P_{\Sigma \to \Omega}: \Sigma^* \to \Omega^*$$

is the operation that removes all events not in  $\Omega$  from a string [RW89]. This operation can be extended to operate on languages as well.

Inverse projection

$$P^{-1}_{\Sigma \leftarrow \Omega}: 2^{\Omega^*} \rightarrow 2^{\Sigma^*}$$

inserts events into all strings at all possible positions [RW89].

According to Simon Ware's report, projection and inverse projection can also be

applied to automata. Projection is implemented by replacing all occurrences of the events to be hidden (the events in  $\gamma$ ) by the *silent* event  $\tau$  first, and then using a determinisation algorithm [HMU01] to make the resultant nondeterministic automaton deterministic. Inverse projection is achieved by adding selfloops with the hidden events to all the states of the automaton. [WM08]

#### 2.5 Model Checker

There are three different kinds of model checkers used in this project to check controllability and language inclusion of the models. These three model checkers are Native model checker [BBFLPP98], [JS06], BDD model checker [BBFLPP98], [REB86] and modular model checker [SW07], [BMM04]. These three model checkers are available in WATERS [WS].

#### 2.5.1 Native Model Checker

The Native model checker is one of the monolithic model checkers and is implemented in Java and refined in C++. It constructs the synchronous product of the model to be checked and explores all of the states of the synchronous product to verify the model. This method describes the state space of the synchronous product of the model explicitly and the memory used to represent the synchronous product directly depends on number of states.

#### 2.5.2 BDD Model Checker

The BDD model checker is a BDD-based model checker and is implemented in Java. BDD means binary decision diagram. A BDD is an ordered graph representation of a Boolean function. The BDD model checker is also one of the monolithic model checkers which constructs the synchronous product of the model to be checked and explores all of the states of the synchronous product. The difference is that the BDD model checker represents the state space symbolically with BDD nodes instead of listing the state space explicitly. The number of BDD nodes is usually smaller than the number of states.

#### 2.5.3 Modular Model Checker

The modular model checker analyses the subsets of the automata of a model instead of checking the entire set of automata of the model at the same time. Since the synchronous product of a model is the intersection of all languages of the language of individual component of the model, if a subset of the specifications of a model is checked to be controllable with respect to a subset of plants of the model, then the entire system cannot contain a counterexample for the subset of specifications and plants. Therefore, it is possible to verify that a specification is controllable or a property is satisfied without composing the entire set of automata of the model.

## 2.6 Examples for Evaluation

A computer with an AMD3200+ (2GHz) CPU and a 2GB RAM is used for testing of this project. The following are the examples used for evaluation. The models of

these examples are available in WATERS [WS].

- big\_bmw is the model of the BMW E65 CAS window lift controller [PD00] [PM03]. bmw\_fh is a small version of it.

- ftechnik, fzelle are about case studies of two different production cells [LL95] [LM96].

- rhone\_alps, and rhone\_tough describe an AIP automated manufacturing system [BC94] [RJL96].

- tbed\_ctct, tbed\_nocoll, tbed\_noderail, tbed\_uncont represent a train testbed [RJL96].

- verriegel4, ftuer, and koordwsp represent a central locking system.

- small\_factory\_2 comes from the classical "small factory" example from [RW89]. bfactory is an upgrade version of small\_factory\_2.

- tictactoe represents a model of a tic tac toe game.

- mx27 represents a case of a maze game.

The above examples are used for controllability check. small\_factory\_2, bfactory, bmw\_fh, ftuer, koordwsp, tictactoe, and mx27 are small examples and the rest of them are large examples with more automata.

models beginning with profisafe represent the PROFIsafe field bus protocol [MM03], [MM02], [PN02].

These models are used for language inclusion check. They are extremely large examples. The verification of example *profisafe\_i6*, which was never solved before, is solved first in this report.

## 2.7 Implementation

This enhanced compositional verification method is implemented in Java and available in WATERS [WS]. The information of classes and data structures is available in [WS]. In order to switch different components selection methods efficiently, this implementation allows a methods selection option from the command line. This implementation also allows options for projection limit, state limit, model checker, and safety properties.

## Chapter 3

## **Enhanced Compositional Verification**

#### 3.1 Introduction

The verification of safety properties is an essential part for ensuring that the model is developed correctly and the model does not contain errors or bugs [CMM05]. Commonly, a model checker composes the entire set of automata of a model to obtain the synchronous product. This can easily cause the state-space explosion problem. Therefore, if a model checker can compose some automata first instead of the entire set of automata of the model, and then simplify the composition, the whole model could become smaller and the state-space explosion problem can be reduced. This strategy is called compositional verification. It composes a subset of the automata of the model first and simplifies the composition with projection [WM08].

One question in compositional verification is how the automata are composed and their events are projected. Different selection strategies and orders can lead to different performance. Hence, the automata selection is a substantial part of compositional verification. This report presents an enhanced compositional verification measure to solve the automata selection problem. The enhanced compositional verification uses a two-step method to select the automata to be composed out of the entire set of automata of the system. One set of selected automata is called a candidate. The candidates are groups of automata sharing the

events that can be removed because they are not used anywhere else but in this group of automata only. The first step is constructing a series of candidates according to a method called mustL [FM06]. The second step is selecting the most proper candidate from the series of candidates according to certain heuristics such as maxL, minS, minT [FM06], and minCut. The candidates construction method and candidates selection methods are discussed in detail in chapter 5. After the candidate is chosen, projection is employed to compose all of the automata in the candidate into one new automaton and project some events out to reduce the size and complexity of this new automaton. This new automaton is added in the model and the set of automata which are composed are removed from the model. Then the model is changed and has a new set of automata. This new set of automata can be composed and projected again with the two-step candidate selection method. In this way, the compositional model verifier can iteratively compose automata of the model and project some events out. Finally, the modified model is passed to a non-projection safety model checker for safety verification.

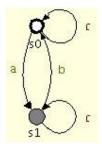

Figure 3.1 Simple process of Enhanced Compositional Verification

Figure 3.1 displays a simple example process of enhanced compositional verification. There is a model with six automata which are plant P1, P2, P3, P4, P5 and specification S. With enhanced compositional verification, P1 and P2 are chosen at the first round, because they share some events which are not used anywhere else. These events, called local events [FM06], can be projected out. After composing P1 and P2 and projecting the local events, a new automaton N1 is created. Then P1 and P2 are replaced by N1 and the model has five automata which are N1, P3, P4, P5 and S. At the second round, N1 and P3 are selected and they have some local events, too. After composing N1 and P3 and projecting out the local events, N2 is created. Then the model has four automata which are N2, P4, P5 and S. At the last round, there is only one candidate which is P5. P5 has one or more local events which can be projected. So P5 can be simplified just by

projecting the local events out and becomes to a new automaton *N3*. Then the original model becomes the simplified model which has four automata which are *N2*, *P4*, *N3* and *S*. Then this simplified model can be verified by a non-projection safety model checker.

### 3.2 Algorithm

The following is the enhanced compositional verification algorithm based on Simon Ware's projection algorithm [WM08]. In this algorithm, the hidden events set is the set of all events mentioned by plant automata only because compositional verification composes plant automata only. The reason is that wrong results may be produced if certain events from the property or specification automata are projected out during compositional verification. A candidate is a set of automata from which a set of events E can be projected because all events in E are local and not used anywhere else.

Let *Plant* be the plant set of the model. Let *Events* be the event set of the model. Let *Hidden* be the set of event that can be projected in the model.

- With *Plant* and *Hidden* as input, find every candidate according to the candidates construction method. Add these candidates into a list of candidates C.

- 2. If *C* is empty, return.

- 3. Select a proper candidate *can* with a set of local events *E* from *C* according to a given heuristic.

- 4. Compose and project *can*. If the maximum state limit for the projection is not exceeded, then a new automaton *aut* is obtained. Otherwise remove *can* from *C* and go to 2.

- 5. Replace the automata of *can* by *aut* in *Plant*. Remove *E* from *Hidden* and *Events*.

Figure 3.2 Candidate Selection and Projection Algorithm

Figure 3.2 presents an algorithm of candidate selection and projection. The events set E is a nonempty set of events and a subset of Hidden. According to the algorithm in Figure 3.2, the events in Hidden are not necessarily removed completely. That is because there is a state limit for the projection. If the number of states of the new composed automaton exceeds the limit, this candidate is not a proper candidate for reducing the size of the model. Therefore, this candidate is dropped and the events supposed to be hidden by this candidate are not hidden. The given heuristics mentioned at step 3 in Figure 3.2 are heuristic maxL, minS,

minT, and minCut.

As for the whole model, the compositional way can be used iteratively in order to make the model as small as possible. The following is the iterative compositional verification algorithm. This algorithm assumes that all events, which are not mentioned by specification automata for controllability check or not mentioned by property automata for language inclusion check, can be projected.

Let *Plant* be the plant set and *Spec* be the specification set of the model. Let *Events* be the event set of the model.

- 1. Let *Hidden* be the set of events used in *Plant* only.

- 2. With *Plant* and *Hidden* as input, do the composing and projection using the algorithm in Figure 3.2 and get the new *Plant*, new *Events* and new *Hidden*.

- 3. If *Plant* and *Hidden* are not changed, go to 4. Else go to 1.

- 4. Create a new model *M* with automata set *Spec* and *Plant*, and events set *Events*.

- 5. Send M to a non-projection safety model checker for analyzing.

Figure 3.3 Iterative Compositional Verification Algorithm

Figure 3.3 presents an iterative algorithm of compositional verification. The idea of this iterative algorithm is continually composing a subset of the automata of the model first and projecting the local events of it to obtain a new automaton, and then replacing this set of automata with the new automaton. Also, for every time

of iteration, the set of automata of the model is different. Hence, the candidate list needs to be reconstructed for every time of iteration.

## 3.3 Counterexample Extension for Projection

The enhanced compositional verification in this report applies projection to improve the performance of verification. Projection simplifies automata by removing some events. However, this method has its drawback. With projection, some events which should in the counterexample trace may be projected, and the trace may not be complete any longer.

If a model has a counterexample trace which contains an event  $\sigma$  before projection, the model must also have the counterexample trace which contains the event  $\sigma$  after projection. However, this event  $\sigma$  could be removed from the model by projection, and the counterexample trace obtained from the model after projection may not a proper trace for the original model. Therefore, there is a need to extend the trace by inserting the  $\sigma$  event back. Fortunately, according to Simon Ware's study, the short counterexample trace can be extended to a complete trace which is a proper trace for the original model by inserting some of the removed events. The following is Simon's algorithm [SW07] [WM08] to find such a trace.

Let t be a counterexample found in the model made of the events  $\sigma_0$ ,  $\sigma_1$  ...  $\sigma_{n-1}$  when n is the length of the trace t, also let A be the original automaton before it is projected. Let Q be a queue of tuples of states in A, length through t, and built-up trace, and let S be a set of pairs of state and length through t, and  $\Sigma$  be the set of kept events.

- 1. Add the tuple (initial state(A), 0, []) to Q and (initial state(A), 0) to S.

- 2. Remove the first tuple (state,i,s) in Q.

- 3. If i = n return s.

- 4. If there is an outgoing transition from *state* labeled with  $\sigma$ i to *next* add  $(next,i+1,s\sigma$ i) to Q and (next,i+1) to S unless  $(next,i+1) \in S$ .

- 5. For every event  $\alpha$  not in  $\Sigma$ , if there is an outgoing transition from *state* labeled with  $\alpha$  to *next*, then add (*next*,*i*,*s* $\alpha$ ) to Q and (*next*,*i*) to S unless (*next*,*i*)  $\in S$ .

- 6. Go to 2.

Figure 3.4: Find Trace Algorithm

This algorithm takes a breadth first search through the original automaton and tries to insert some events which are removed by projection into the projected counterexample trace in order to make this counterexample trace acceptable by the original automaton. In other words, this algorithm runs the incomplete trace in the original automaton and inserts the proper missing events which are from the removed events into the trace. If the current event of the trace is enabled in the current state of the automaton, it remains the current event of the trace. Otherwise, if all events are tried in the current state, try the events which are hidden. Find all hidden events which are enabled in the current state and try each of them until

reach an event in the incomplete trace. Those events appear only in this automaton and do not appear in any other automata, so they can be inserted anywhere into the trace and other automata cannot reject the trace.

If the model is iteratively projected, the following algorithm is adopted to find a proper counterexample trace.

Let  $A_1, ..., A_n$  be the automata simplified by iterative projection, and let  $\Sigma_i$  be the set of events  $A_i$  is projected with respect to, and let t be the projected trace.

- 1. Set i to equal n.

- 2. If i equals 0 return t.

- 3. Find the trace s using the algorithm in Figure 3.4 with  $A_i$  and  $\Sigma'_i$  as input.

- 4. Set the new value of t to s, and decrement i, then go to 2.

Figure 3.5: Iterative Find Trace Algorithm

This algorithm is based on the algorithm in Figure 3.4. It uses a backward strategy to extend the trace. It starts from the last automaton, which is projected to the first automaton. This algorithm needs to know which set of events are projected from which set of automata.

## **Chapter 4**

## **Automata Transformation**

Compositional verification with projection can effectively reduce the state-space explosion problem [RW89], but there are still some models which are too large to be verified. In order to reduce the state-space explosion problem further and take more advantage of compositional verification, it is necessary to employ more strategies to cut down the size of models.

This chapter presents two types of strategies to improve the performance of projection and reduce the size of automata. These two types of strategies are Automata Conversion [SW07], [WM08] and Automata Simplification. Automata Conversion converts specifications into plants for controllability check, and properties into non-properties for language inclusion check to remove some events, which are used in specifications or properties. Automata Simplification tries to simplify the individual automaton by removing or replacing some unnecessary events.

Also, the counterexample trace is changed and not accepted by the original model anymore after Automata Conversion and Almost Same Transition Check in Automata Simplification. This chapter describes some methods to correct the trace.

## 4.1 Automata Conversion

#### 4.1.1 Introduction

According to Simon Ware's paper, Automata Conversion converts the model into a new model which has more events that can be hidden and reduce the state-space explosion problem further by adding some selfloop events. Furthermore, after Automata Conversion, the model is easier for safety verification.

Simon Ware [SW07], [WM08] presents a strategy of translating the controllability problem into a language inclusion problem for the standard controllability check. As for controllability check, Automata Conversion converts the standard controllability problem into a language inclusion problem. In this way, this strategy not only can project more controllable events which are used in specifications, but also converts the problem of checking if uncontrollable events can happen at an improper time into a much simpler problem of checking if certain bad events can happen [SW07].

Since Automata Conversion works for controllability check, it should also have the probability of working for language inclusion check. Therefore, this project presents an Automata Conversion method for language inclusion check. As for language inclusion check, Automata Conversion converts the language inclusion problem into another language inclusion problem. The difference between these

two problems is that more events can be projected in the model after Automata Conversion.

### 4.1.2 Automata Conversion for Controllability Check

As for controllability check, Simon Ware's method converts the plant P and the specification S in the original model into a plant P' and a specification S' by adding new  $\gamma$  events into the model such that for all the specifications  $S_i$  and uncontrollable events  $v_j$ , the event  $\gamma_{ij}$  can happen only in a situation where  $v_j$  is allowed by P but not allowed by  $S_i$  [SW07], [WM08]. The following describes how to convert the specification automata and plant automata.

#### **4.1.2.1** Specification Automata Conversion

For every uncontrollable event  $v_j$  and for all states s in specification  $S_i$ , if there is no outgoing transition labeled with  $v_j$  in s, add the selfloop transition (s,  $\gamma_{ij}$ , s). In a specification automaton, the  $\gamma$  events that are added have nothing to do with other specification automata.

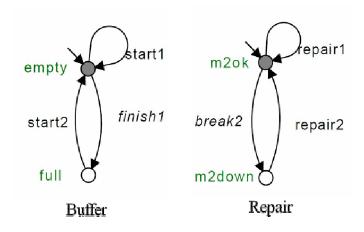

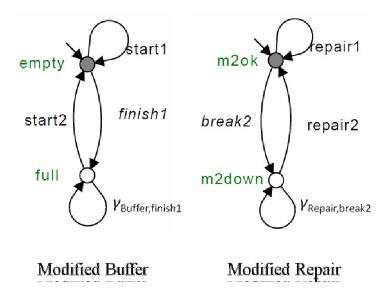

Figure 4.1: Specification Buffer and Repair

Figure 4.1 displays two specifications of the model *small\_factory\_2* which are *Buffer* and *Repair*. This model comes from the classical "small factory" example from [RW89]. In specification *Buffer*, there is only one uncontrollable event *finish1*. In specification *Repair*, there is only one uncontrollable event *break2*. The rest of the events in these two specification automata are controllable. Then, according to the specification Automata Conversion algorithm above, these two specifications are converted to the modified automata displayed in Figure 4.2.

Figure 4.2: Modified Specification Buffer and Repair

In *Buffer*, there are two states which are *empty* and *full*, and one uncontrollable event *finish1*. In state *empty*, there exists an outgoing transition (*empty*, *finish1*, *full*) labeled with *finish1*. So the  $\gamma$  event is not added in this state. But in state *full*, there is no outgoing transitions labeled with uncontrollable event *finish1*. Therefore, a selfloop transition (*full*,  $\gamma_{\text{Buffer,finish1}}$ , *full*) is added to this state.

In *Repair*, there are two states which are m2ok and m2down, and one uncontrollable event break2. As for the uncontrollable event break2 in state m2ok, there exists an outgoing transition (m2ok, break2, m2down) labeled with break2. So the  $\gamma$  event is not added in this state. But in state m2down, there is no outgoing transition labeled with uncontrollable event break2. Therefore, a selfloop transition (m2down,  $\gamma_{Repair,break2}$ , m2down) is added to this state.

#### 4.1.2.2 Plant Automata Conversion

After the conversion of specification automata, a set of  $\gamma$  events are obtained. The

plant automata also need to be converted by adding some  $\gamma$  events in order to make the model equivalent to the original model. The following is the method of plant Automata Conversion.

For every uncontrollable event  $v_j$ , which also is mentioned by specifications, and for all states s in plant  $P_k$ , if there is an outgoing transition labeled with  $v_j$  in s, then add the selfloop transition  $(s, \gamma_{ij}, s)$  for every possible i. Hence, once the plant  $P_k$  allows the event  $v_j$ , it will also allow any event  $\gamma$  related to  $v_j$  [SW07], [WM08].

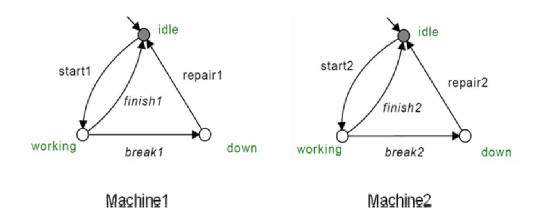

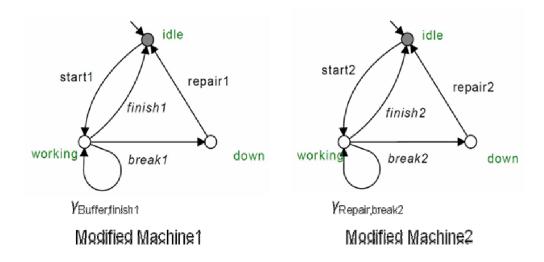

Figure 4.3: Plant Machine1 and Machine2

Figure 4.3 displays two plant automata, which are Machine1 and Machine2, of the model  $small\_factory\_2$ . There is one uncontrollable  $v_j$  event, which is finish1, in plant Machine1. Also, in plant Machine2, there is one uncontrollable  $v_j$  event break2. Then, these two plant automata are converted to the following modified automata according to the plant Automata Conversion method.

Figure 4.4: Modified Plant Machine1 and Machine2

Figure 4.4 displays the modified plant automata of *Machine1* and *Machine2*. In plant *Machine1*, there are three states, which are *idle*, *working*, and *down*, and one uncontrollable  $v_j$  event, which is *finish1*. In state *idle* and *down*, there is no outgoing transition labeled with uncontrollable  $v_j$  event *finish1*. Hence, the  $\gamma$  event is not added into these two states. In state *working*, there is an outgoing transition (*working*, *finish1*, *idle*) labeled with uncontrollable  $v_j$  event *finish1*. So a selfloop transition (*working*,  $\gamma_{\text{Buffer,finish1}}$ , *working*) is added to this state.

In plant *Machine2*, the situation is similar. In state *idle* and *down*, there is no outgoing transition labeled with uncontrollable  $v_j$  event *break2*. Hence, the  $\gamma$  event is not added into these two states. In state *working*, there is an outgoing transition (*working*, *break2*, *down*) labeled with uncontrollable  $v_j$  event *break2*. So a selfloop transition (*working*,  $\gamma_{\text{Repair,break2}}$ , *working*) is added to this state.

#### 4.1.2.3 One-state specification creation

After the conversion of specifications and plants, the  $\gamma_{ij}$  events can happen if and

only if the uncontrollable  $v_j$  events are enabled in all plants but disabled in specification  $S_i$ . Therefore, as for controllability check, the modified specification automata are treated as plant automata and a one-state specification is created for the checking.

The one-state specification automaton contains a single state and a set of blocked events which are the  $\gamma$  events. Figure 4.5 displays such a specification of model  $small\_factory\_2$ . The main aim of this one-state specification is to tell the controllability checker that the  $\gamma$  events should not happen. For instance, in Figure 4.5, event  $\gamma_{Buffer,finish1}$  and event  $\gamma_{Repair,break2}$  are not enabled in any states and can never happen.

## One-state Specification

Figure 4.5: An Example One-state Specification

#### 4.1.2.4 Evaluation

This test uses the heuristic minS for the second step of candidate selection and the projection limit is 1000. The non-projection model checker used for the checking

is the Modular Controllability Checker. The examples used in the evaluation are from [PD00], [PM03], [LL95], [LM96], [BC94], [RJL96].

| Model           | With composing and projection |        |         |        | nodel conv | ,       | γ<br>Events | R<br>Events | Original<br>Events |

|-----------------|-------------------------------|--------|---------|--------|------------|---------|-------------|-------------|--------------------|

|                 | States                        | Events | Time(s) | States | Events     | Time(s) | Lvents      | Lvents      | Lvents             |

| big_bmw         | 168                           | 66     | 0.304   | 6      | 47         | 0.683   | 47          | 66          | 66                 |

| Ftechnik        | 374297                        | 117    | 2.408   | 24     | 156        | 5.479   | 117         | 117         | 117                |

| Fzelle          | 1448                          | 82     | 0.670   | 4      | 113        | 1.610   | 113         | 82          | 88                 |

| rhone_alps      | 1540                          | 74     | 0.416   | 2      | 38         | 0.590   | 38          | 74          | 90                 |

| rhone_tough     | О                             | 76     |         | 366141 | 74         | 8.517   | 40          | 76          | 98                 |

| tbed_ctct       | 1057536                       | 88     | 4.452   | О      | 200        |         | 131         | 88          | 116                |

| tbed_nocoll     | 81522                         | 88     | 1.057   | 43976  | 190        | 15.641  | 138         | 88          | 116                |

| tbed_noderail   | 1308927                       | 88     | 5.718   | 43572  | 190        | 14.863  | 138         | 88          | 122                |

| tbed_uncont     | 470752                        | 88     | 3.326   | 8083   | 190        | 16.006  | 138         | 88          | 116                |

| small_factory_2 | 10                            | 6      | 0.296   | 2      | 2          | 0.264   | 2           | 6           | 8                  |

| Bfactory        | 19                            | 5      | 0.297   | 1      | 2          | 0.264   | 2           | 5           | 12                 |

Table 4.1: Automata Conversion Results for Controllability Check

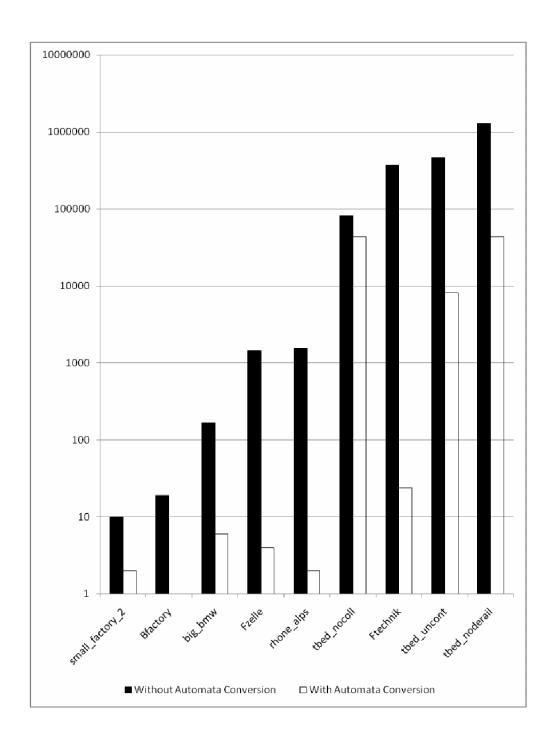

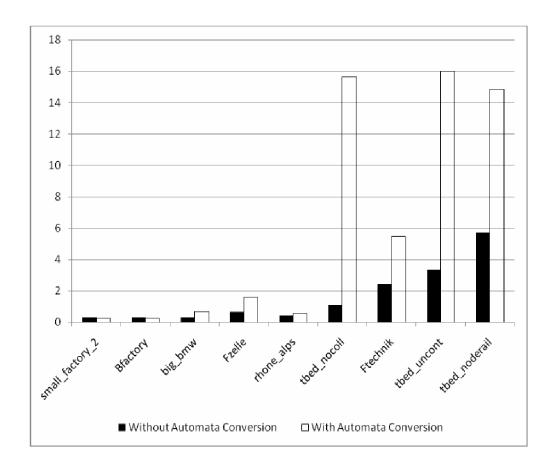

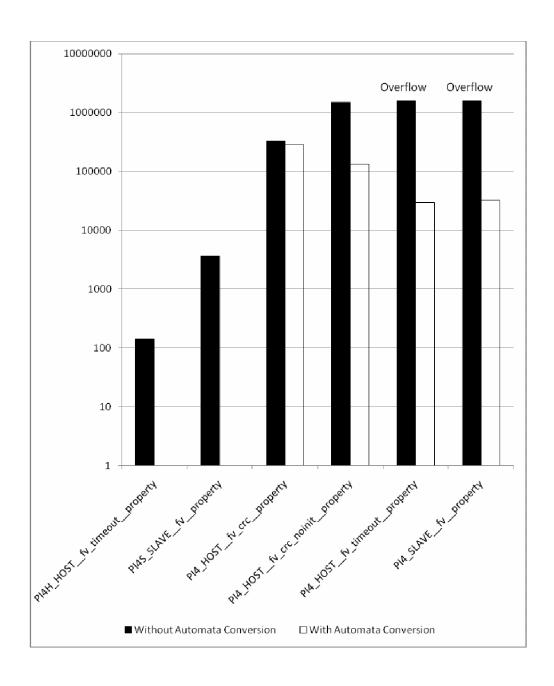

Figure 4.6: Peak number of States after projection with and without Automata Conversion

Figure 4.7: Controllablity Check Processing time with and without Automata Conversion

Table 4.1 displays two test cases. The first case is to check the model with composing and projection. The second case is to check the model with Automata Conversion, composing and projection. The content of the test includes six parts which are States, Events, Time,  $\gamma$  Events, R Events, and Original Events. States is the peak number of the states of the synchronous product of the model after projection that the Modular Controllability Checker explores during the verification. Events is the amount of events of the model after projection. The Time is the processing time of the model checking.  $\gamma$  Events is the created events during Automata Conversion. R Events is the events that shared by plants and

specifications. Original Events is the events of the model without Automata Conversion.

According to Table 4.1, the synchronous product of the model after projection with Automata Conversion is smaller than the model without Automata Conversion. For example, as for model ftechnik [LL95], [LM96], the number of states explored by the model checker without Automata Conversion is 374297, which is fifteen thousand times larger than the number of states explored by the model checker with Automata Conversion which is 24. Furthermore, as for the model rhone\_tough [BC94], [RJL96], it cannot be solved without Automata Conversion. But it can be solved with Automata Conversion. According to Figure 4.6, with the increase of the peak number of states, the effect of Automata Conversion is much more observable. The peak number of states is much smaller after Automata Conversion. The number of events can also be cut down, if the model is small enough and the local events can be projected mostly or completely. For example, the model *small\_factory\_2* [RW89] and *bfactory* are quite small and their numbers of events of the model with Automata Conversion, composing and projection are 3 and 2 respectively which are smaller than their numbers of events of the model without Automata Conversion, which are 6 and 5 respectively. In these two models, the numbers of R Events are 6 and 5 respectively, and the numbers of  $\gamma$  Events are 2 and 2 respectively. Therefore, without Automata Conversion, there are at least 6 events remaining for model *small\_factory\_2* and 5 events remaining for model *bfactory*. With Automata Conversion, there are at least 2 events remaining for mdoel *small\_factory\_2* and 2 events remaining for model bfactory. That is to say, as for model small\_factory\_2, there are four more events which are projected, and as for model *bfactory*, there are three more events which are projected. But often, the number of events increases. That is because the number of events that the Automata Conversion creates is much more than the

number of events that cannot be projected before but can be projected after. For instance, as for model *tbed\_nocoll* [RJL96], its γ Events number is 138 while its original events number is 116. That is to say, the number of events created is 138 and the number of events of the model after projection is at least 138, which is larger than the number of events of the original model. Figure 4.7 shows the result of the processing timewith and without Automata Conversion. The model checking processing timeof the model with Automata Conversion is longer than the processing timeof the model without Automata Conversion. The reason of slow checking time is because there are more projection after Automata Conversion and projection is time consuming.

As a result, the Automata Conversion strategy can reduce the state-space problem and project more events for controllability check, but it needs a longer process time. Furthermore, some models can only be solved with Automata Conversion.

# 4.1.3 Automata Conversion for Language Inclusion Check

Since the controllability problem can be converted into a language inclusion problem and more events can be projected, a language conclusion problem can also has the possibility of being converted into another language inclusion problem in order to remove more events. Instead of removing more controllable events, which are used in specification automata, this strategy removes more events which are enabled in all states of property automata. However, this strategy only suits for the model with a property automaton which has some events that are enabled in all states of the property automaton.

#### **4.1.3.1 Property Automata Conversion**

For every event  $v_j$  which is not enabled in all states and for all states s in property  $R_{i,j}$  if  $v_j$  is not enabled in s, then add the selfloop transition  $(s, \gamma_{ij}, s)$  to s.

# **Property**

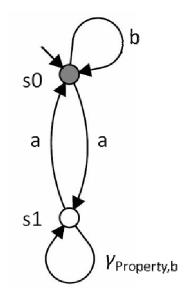

Figure 4.8: An example property

Figure 4.8 displays an example property. This property automaton has two states which are s0 and s1, and two events which are events a and b. Event a is enabled in all states and event b is only enabled in state s0. According to the property Automata Conversion algorithm, this property is converted into the modified property in Figure 4.9.

## **Modified Property**

Figure 4.9: Modified Property

In the property automaton *Property*, there is one event b which is not enabled in all states. As for event b, it is enabled in state s0. So the  $\gamma$  event is added in state s0. In state s1, event b is not enabled. So the selfloop transition  $(s1, \gamma_{\text{Property,b}}, s1)$  is added to this state.

### 4.1.3.2 Non-property Automata Conversion

For every event  $v_j$ , which is not enabled in all states of the property automaton, and for all states s in non-property automaton  $NP_i$ , if event  $v_j$  is enabled in s, then add the selfloop transition  $(s, \gamma_{ij}, s)$  for every possible non-property automaton  $NP_i$ . Hence, once the non-property automaton  $NP_i$  allows the event  $v_j$ , it will also allow any event  $\gamma$  related to  $v_j$ .

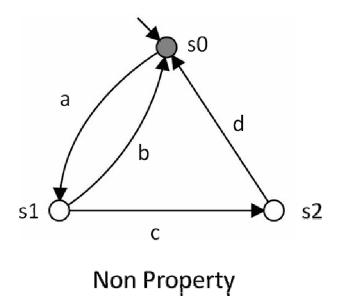

Figure 4.10: An example Non-Property

Figure 4.10 displays an example non-property automaton. This automaton has three states which are s0, s1, and s2, and four events which are event a, b, c, and d. Thereinto, event b is not enabled in all states of property *Property*. According to the non-property Automata Conversion, the automaton in Figure 4.8 is converted into the modified automaton in Figure 4.11.

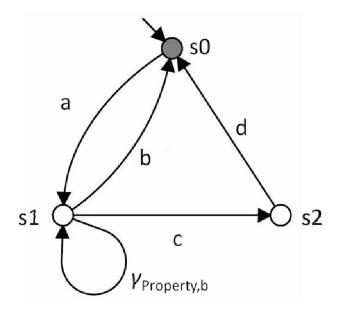

# **Modified Non Property**

Figure 4.11: Modified Non-Property

In the non-property automaton, there is one event b which is not enabled in all states of property *Property*. As for event b, it is not enabled in state s0 and s2. So the  $\gamma$  event is not added in state s0 and s2. In state s1, event b is enabled. So the selfloop transition  $(s1, \gamma_{\text{Property,b}}, s1)$  is added to this state.

#### 4.1.3.3 One-state property creation

After the conversion of property automata and non-property automata, the modified property automata are treated as non-property automata and a one-state property is created for the checking. The one-state property automaton contains a single state and a set of blocked events which are the  $\gamma$  events. Figure 4.12 displays such a property. In this one-state property, event  $\gamma_{\text{Property,b}}$  is not enabled in any states and shall never happen.

## **BLOCKED:**

V<sub>Property,b</sub>

## **One-state Property**

Figure 4.12: An example One-state Property

#### 4.1.3.4 Evaluation

This test takes the heuristic minS for the second step of candidate selection and the projection limit is 1000. The non-projection model checker used for the checking is the BDD Language Inclusion Checker. The examples used in this evaluation are from the PROIsafe field bus protocol [MM03], [MM02], [PN02].

| Model                 | Property                           | With composing and projection |        |         | With model conversion, composing and projection |        |         | OE  | EE | γE | RE |

|-----------------------|------------------------------------|-------------------------------|--------|---------|-------------------------------------------------|--------|---------|-----|----|----|----|

|                       |                                    | Nodes                         | Events | Time(s) | Nodes                                           | Events | Time(s) |     |    |    |    |

| profisafe<br>_i4_host | HOST_fv _timeout _property         | 141                           | 4      | 11.169  | 1                                               | 1      | 7.192   | 218 | 3  | 1  | 4  |

| profisafe             | SLAVE_fv                           |                               |        |         |                                                 |        |         |     |    |    |    |

| _i4_slave             | property                           | 3642                          | 32     | 2.825   | 1                                               | 21     | 1.512   | 130 | 11 | 21 | 32 |

| profisafe<br>_i4      | HOSTfv                             | 220116                        | 105    | 29,543  | 288624                                          | 120    | 59,734  | 393 | 82 | 1  | 83 |

|                       | property  HOSTfvcrc_noinitproperty | 330116<br>1498633             | 201    | 90.120  | 134107                                          | 120    | 198.867 | 393 | 83 | 1  | 84 |

|                       | HOSTfv _timeoutproperty            | 0                             | 99     |         | 29982                                           | 32     | 16.435  | 378 | 3  | 1  | 4  |

|                       | SLAVE_fvproperty                   | 0                             | 47     |         | 32499                                           | 37     | 16.606  | 378 | 11 | 6  | 17 |

Table 4.2: Automata Conversion Results for Language Inclusion Check

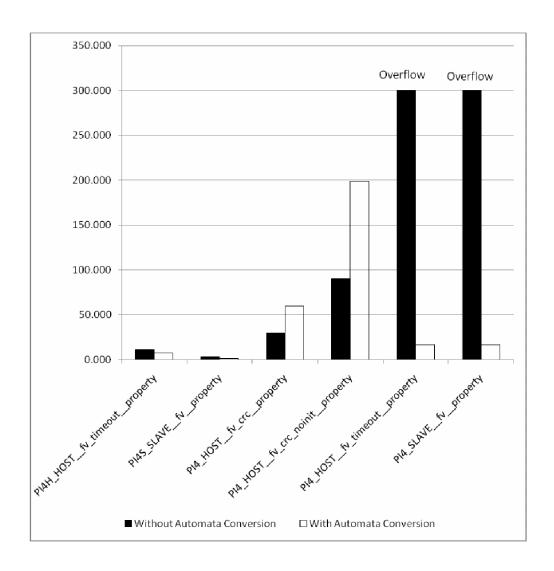

Figure 4.13: Peak number of Nodes after projection with and without Automata Conversion

Figure 4.14: Language Inclusion Check Process Time with and without Automata Conversion

Table 4.2 displays two test cases. The first case is to check the model with composing and projection. The second case is to check the model with Automata Conversion, composing and projection. The content of the test includes three parts which are Nodes, Events, and Time. Nodes is the peak number of the nodes of the synchronous product of the model after projection that the BDD language inclusion checker explores. Events is the number of events of the model after projection. Time is the processing timefor the model checking. Also, Table 4.2

displays other four parts for evaluation which are OE, EE,  $\gamma$ E, and RE. OE is the number of original events of the original model. EE is the number of events enabled in all states of the property which can be hidden after the Automata Conversion.  $\gamma$ E is the  $\gamma$  events created during Automata Conversion. RE is the related events shared by both property automata and non-property automata. There is only one property in each example.

According to Table 4.2, the peak number of nodes explored by the BDD checker after projection with Automata Conversion is smaller than the peak number of nodes after projection without Automata Conversion. For example, as for model profisafe\_i4\_host with the property HOST\_\_fv\_timeout\_\_property, the peak nodes number of the synchronous product of the model without Automata Conversion is 139289, which is one hundred and forty thousand times larger than the peak nodes number of the synchronous product of the model with Automata Conversion which is 1. Furthermore, as for the model *profisafe\_i4*, it is not solved without Automata Conversion when checking the property *HOST\_fv\_timeout\_property* and the property SLAVE\_fv\_property. But it is solved with Automata Conversion. According to Figure 4.13, Automata Conversion works well with large examples. The events number can be cut down even though there are many  $\gamma$ events that are created. However, the difference of the model checking processing timebetween the check with Automata Conversion and the check without Automata Conversion cannot be defined because of the different situation of the model. If the proportion of time for projection is higher in the entire check process time, then the entire check processing timewithout Automata Conversion is faster than the entire check processing timewith Automata Conversion because the model check with Automata Conversion has more projection.

As a result, the Automata Conversion strategy can reduce the size of the

synchronous product of the model and project more events for language inclusion check. Furthermore, some models can only be solved with Automata Conversion.

# 4.1.4 Counterexample Correction for Automata Conversion

Automata Conversion can be used to project more events and make the model smaller. But this method has a drawback of modifying the counterexample. The counterexample trace contains one new  $\gamma$  event which cannot be accepted by the original model. Therefore, the counterexample trace needs to be fixed.

The key strategy of automaton conversion is to build a singleton state specification automaton or property automaton with some new uncontrollable  $\gamma$  events which are created according to the original specification automata or property automata. In this singleton state automaton, these new uncontrollable  $\gamma$  events must not happen. In this way, the converted model is failed to pass the safety verification once one of these  $\gamma$  events happens. That is to say, the last event in the counterexample trace must be one of these new uncontrollable  $\gamma$  events. Therefore, the counterexample is changed and there is only one  $\gamma$  event needs to be renovated.

Therefore, the source events, which the creation of new events relies on, need to be remembered when the automaton conversion proceeds. Thus, a map which takes the source events as key and the new events as value is built to track down the original events of the new events. Then, use the original event to replace the new event at the end of the counterexample trace and finish the counterexample correction for automaton transformation.

Let M be the map of storing source event  $\alpha_i$  and new event  $\beta_i$  pairs. Let t be the counterexample trace and n be the length of trace t.

- 1. Find the last event  $\beta_i$  of t which is at position n-1.

- 2. Find the source event  $\alpha_i$  of new event  $\beta_i$  according to M.

- 3. Replace the new event  $\beta_i$  with the source event  $\alpha_i$  in trace t, and return t.

Figure 4.15: Counterexample Correction Algorithm for Automata Conversion

## 4.2 Automata Simplification

### 4.2.1 Introduction

All of the experimental data show that, the smaller automata are, the faster composing and projection are executed. Therefore keeping the automata as small as possible is vital not only for composing and projection, but also for verification. Especially for large models, they need composing and projection more than small models because of their huge sizes and complexity. However, many automata are not small and simple enough because of bad design or as a result of projection. For example, after projection, some states are amalgamated into one state. Hence, some transitions which originally have different sources or targets may share the same sources and targets after projection. Then those transitions may become unnecessary and not influence the result of verification. Consequently, they can be removed or replaced in order to keep the automata as small and simple as possible. The following are three aspects to simplify automata.

## **4.2.2** Selfloop Check

In an automaton, if an event is enabled at all states and used by selfloop only, this event and selfloops can be removed in this automaton.

Figure 4.16: An example of Selfloop Check

For the example above, event *x* is enabled in all states and it is removed in this automaton. So are the selfloops labeled with event *x*.

Furthermore, if event x only ever is used as selfloop events, and event x is controllable or it is used in plants only, then event x can be removed, too. The reason is that controllability verification is only interested in uncontrollable events in specifications, and event x cannot change the state because it is a selfloop event. Therefore, the result of verification cannot be influenced by removing such an event.

## 4.2.3 Same Transition Check

If two or more events are only enabled together (they share the source and target) in all automata, they are called same transition. They can be replaced by a single

event.

Figure 4.17: An example of Same Transition Check

For the example in Figure 4.17, this model has three automata which are A, B, and C. Event a and event b are only enabled together in them. Then event a and b are same transition and they can be replaced by a single event.

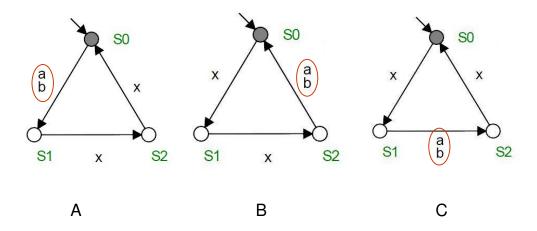

## 4.2.4 Almost Same Transition Check

If two or more events are only enabled together (they share the source and target) in all automata except one automaton, they are called Almost Same Transition. They can be replaced by a single event. The automaton in which the events are not enabled together is called an Almost Same Transition Automaton.

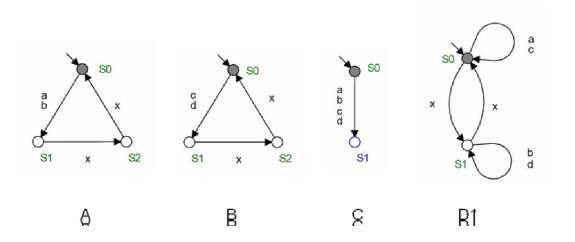

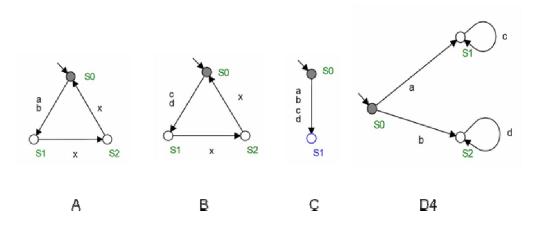

Figure 4.18: An example of Almost Same Transition Check

For the example in Figure 4.18, this model has four automata which are A, B, C, and D1. Events a and b are only enabled together in A, B (hidden selfloop), and C but not D1. So they are Almost Same Transition and can be replaced by a single event. So are events c and d. And D1 is the Almost Same Transition Automaton for events a and b. As for events c and d, D1 is the Almost Same Transition Automaton, too. As for a real model, the Almost Same Transition Automaton can be different and more than one.

Figure 4.19: Nondeterminism Problem of Almost Same Transition Check

However, if those events share the same source in this particular automaton, they cannot be Almost Same Transition. That is because if they are replaced by a single event, then the automaton will become nondeterministic. For the example in Figure 4.19, events a and b share the same source state s0 in automaton b4. If they were replaced by a single event e for instance, there are two different successor states for state s0 and event e. This is not supported by non-projecting model checkers used in this project. Thus, this case cannot be treated as an instance of Almost Same Transition.

# **4.2.5** Counterexample Correction for Almost Same Transition Check

Almost Same Transition Check is the only automaton simplification strategy which changes the counterexample trace in the automaton simplification section. The point of Almost Same Transition Check is replacing some events with a new single event in a certain automaton. Hence this strategy does not change the length of the counterexample trace but changes the events of the trace. Also, there may be more than one group of events which can be replaced in one automaton. Therefore, the correction of such a counterexample trace is to find the new events in the trace and replace them with the original events replaced by them.

In order to replace the new events in the counterexample trace with the original events, it is necessary to build a map M to store the replacement information. The construction of M can be done during the Almost Same Transition Check. For instance, in Figure 4.18, the Almost Same Transition Automaton is D1 and there are two sets of events replaced in D1. If events a and b are replaced by a single event e, and events e and e are replaced by a single event e, the map e is

$$M: e \mapsto \{a, b\}$$

$f \mapsto \{c, d\}$

The following is the algorithm of counterexample correction for events replacement in Almost Same Transition check.

Let t be a counterexample found in the model with Almost Same Transition Check made of the events  $\sigma_0$ ,  $\sigma_1$  ...  $\sigma_{n-1}$  when n is the length of the trace t, also let A be the Almost Same Transition Automaton. Let M be the replacement map which stores what new events replace what original events.

- 1. Set the current state *state* to the initial state of automaton A and i to 0.

- 2. If  $\sigma_i$  is enabled in *state*, then set current state *state* to the successor of *state* with event  $\sigma_i$ . Go to 4.

- 3. If  $\sigma_i$  is a new event then look up  $\sigma_i$  in M to find an original event which is enabled in *state*. Set *state* to the successor of *state* with event  $\sigma_i$ .

- 4. Increase *i*. If i = n return *t*.

- 5. Go to 2.

Figure 4.20: Find Replaced Events Algorithm

This algorithm only works for deterministic models. Also, the Almost Same Transition Check states that the group of events which are replaced cannot occur at the same place and cannot have the same source states, either. Hereby, if the counterexample trace has a new event, this event can be replaced by only one

original event. That is to say, in the current state, if there is an outgoing transition labeled with the new event, there is at least one outgoing transition labeled with the original events which are replaced by the new event. The original events may be more than one, but there is at least one event than can bring the system to the same state as the counterexample.

As for a whole model, there may be more than one Almost Same Transition automaton. Also, the Almost Same Transition Check happens after every projection. The following algorithm is for such a trace correction.

Let  $A_1, ..., A_n$  be the Almost Same Transition automata, and let M be the replacement map which stores what new events replace what original events, and let t be the trace with Almost Same Transition check.

- 1. Set i to equal 0.

- 2. If i equals n+1 return t.

- 3. Correct the trace t using the algorithm in Figure 4.20 with  $A_i$  and M as input.

- 4. Increase i, then go to 2.

Figure 4.21 Counterexample Correction Algorithm for Almost Same Transition Check

This algorithm is based on the algorithm in Figure 4.20 and needs to remember what new events replace what original events in what automata.

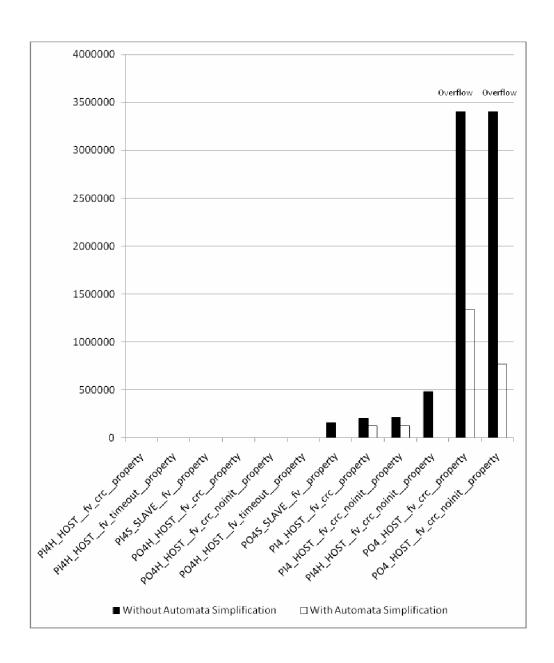

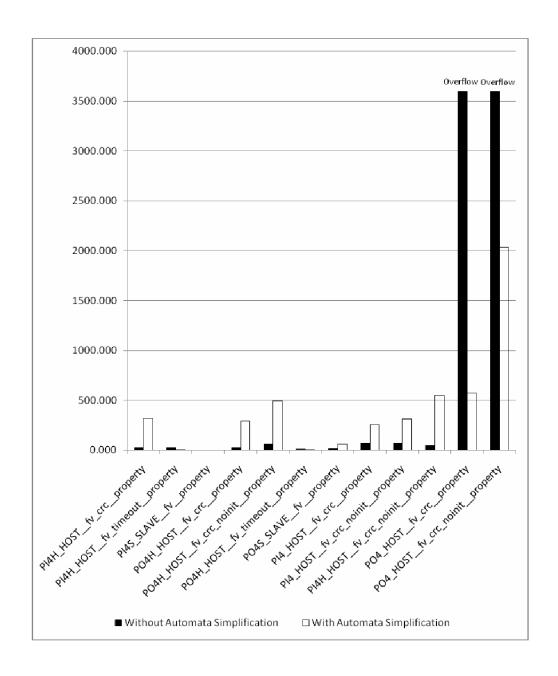

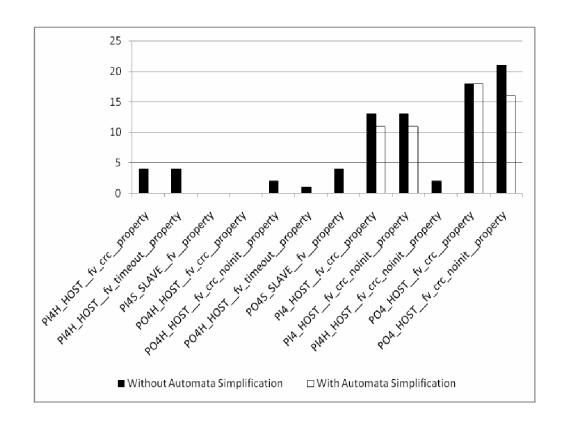

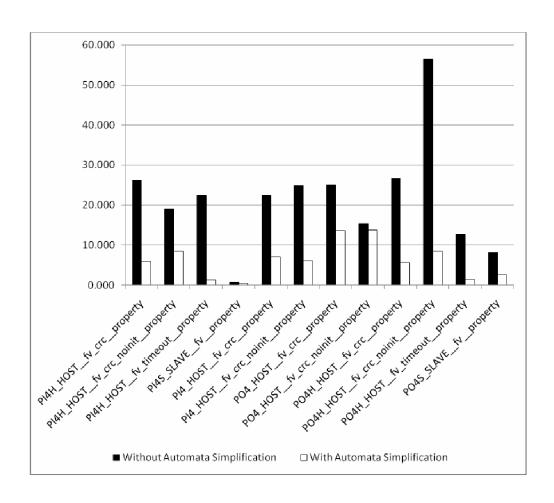

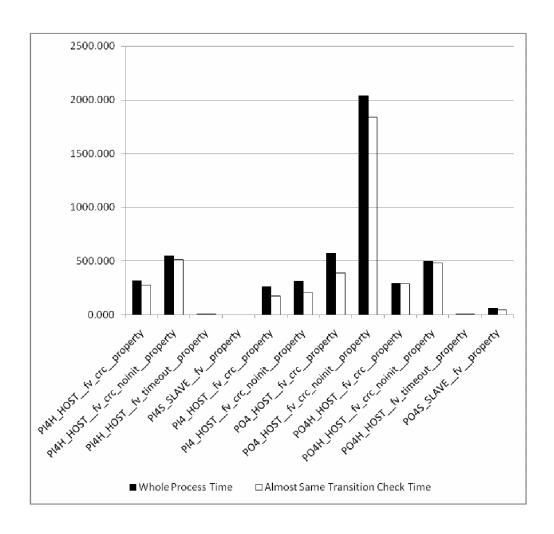

### 4.2.6 Evaluation

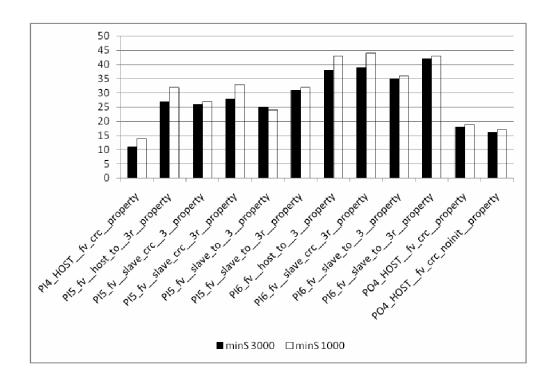

This test takes the heuristic minS for the second step of candidate selection and the projection limit is 3000. The non-projection model checker used for the checking is the BDD Language Inclusion Checker. The examples used in this evaluation are from the PROIsafe field bus protocol [MM03], [MM02], [PN02].

|                    | Property                  |   | Without Automata |         |    | With Automata  |          |    |  |

|--------------------|---------------------------|---|------------------|---------|----|----------------|----------|----|--|

| Model              |                           |   | Simplification   |         |    | Simplification |          |    |  |

|                    |                           |   | Nodes            | Time(s) | 0  | Nodes          | Time(s)  | О  |  |

|                    | HOSTfv_crcproperty        | F | 1                | 30.915  | 4  | 1              | 320.586  | 0  |  |

| profisafe_i4_host  | HOSTfv_crc_noinitproperty |   | 482583           | 51.816  | 2  | 1              | 550.825  | 0  |  |

|                    | HOSTfv_timeoutproperty    | Т | 1                | 26.063  | 4  | 1              | 7.333    | 0  |  |

| profisafe_i4_slave | SLAVE_fv_property         | Т | 1                | 1.174   | 0  | 1              | 1.431    | 0  |  |

| profisafe_i4       | HOSTfv_crcproperty        |   | 200701           | 70.888  | 13 | 127134         | 260.39   | 11 |  |

|                    | HOSTfv_crc_noinitproperty | F | 213800           | 74.151  | 13 | 125906         | 313.274  | 11 |  |

| G . C . A          | HOSTfv_crcproperty        | F |                  | О       | 18 | 1336962        | 575.188  | 18 |  |

| profisafe_o4       | HOSTfv_crc_noinitproperty | F |                  | О       | 21 | 769108         | 2037.814 | 16 |  |

| profisafe_o4_host  | HOSTfv_crcproperty        | F | 1                | 27.312  | 0  | 1              | 295.411  | 0  |  |

|                    | HOSTfv_crc_noinitproperty | Т | 1                | 60.223  | 2  | 1              | 497.484  | 0  |  |

|                    | HOSTfv_timeoutproperty    | T | 1                | 14.95   | 1  | 1              | 7.908    | 0  |  |

| profisafe_o4_slave | SLAVE_fv_property         | Т | 155472           | 19.571  | 4  | 1              | 62.745   | 0  |  |

Table 4.3: Language Inclusion Check Results with and without Automata Simplification

Figure 4.22: Peak Nodes after projection with and without Automata Simpilification

Figure 4.23: Language Inclusion Check Process Time with and without Automata Simplification

Figure 4.24: Projection Overflows with and without Automata Simplification

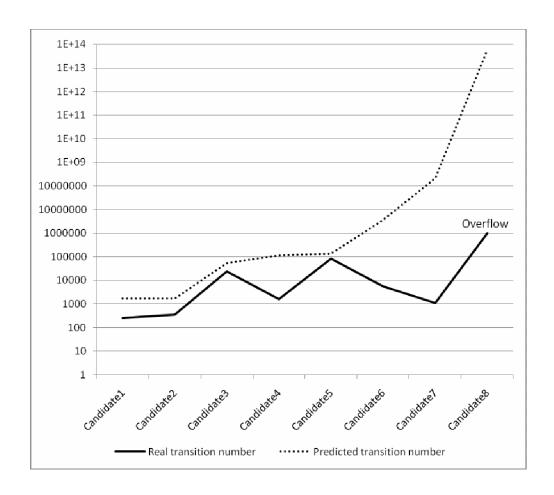

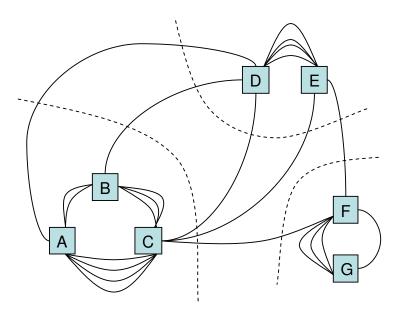

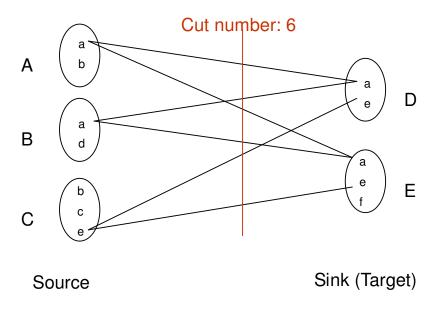

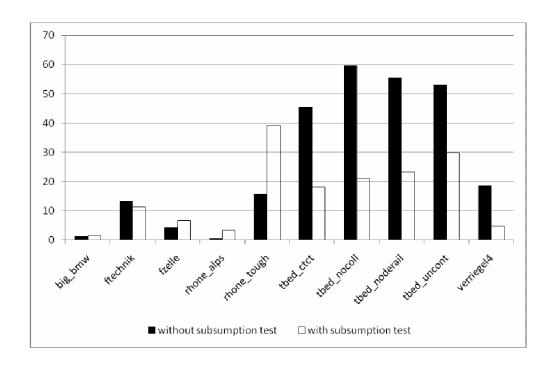

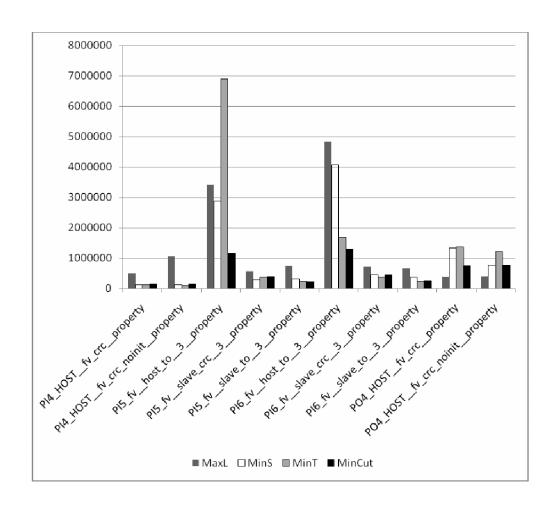

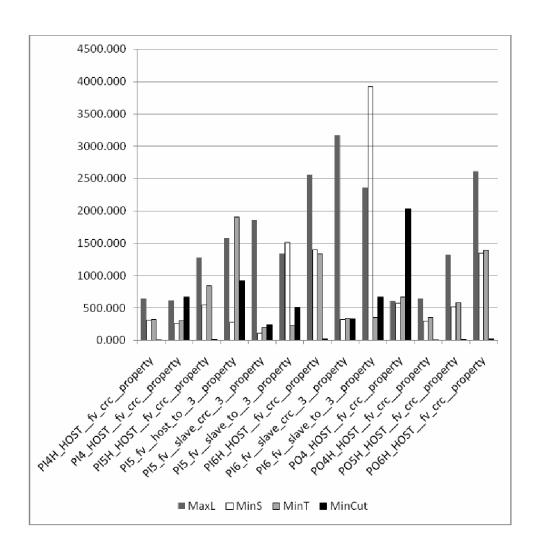

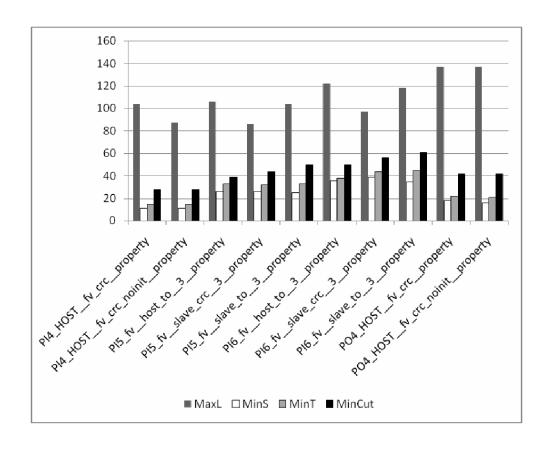

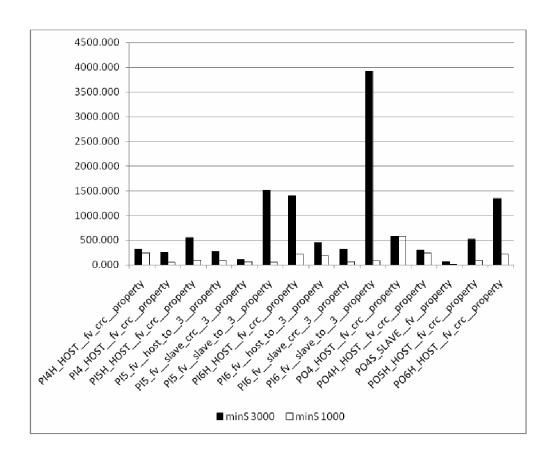

Table 4.3 displays two test cases. The first case is to check the model without Automata Simplification. The second case is to check the model with Automata Simplification. The content of the test includes three parts which are Nodes, Time, and O. The Nodes is the peak number of the nodes of the synchronous product of the model after projection that the BDD language inclusion checker explores. The Time is the processing timefor the model checking. The O states the overflows of projection. Furthermore, there is only one property in each example.